# System Architecture Reference Guide

Rev. 21.0

DOC9473-2LA

# System Architecture Reference Guide

**Second Edition**

by Marilyn Hammond

Prime Computer, Inc. Prime Park Natick, Massachusetts 01760 The information in this document is subject to change without notice and should not be construed as a commitment by Prime Computer, Inc. Prime Computer, Inc., assumes no responsibility for any errors that may appear in this document.

The software described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license.

Copyright © 1987 by Prime Computer, Inc. All rights reserved.

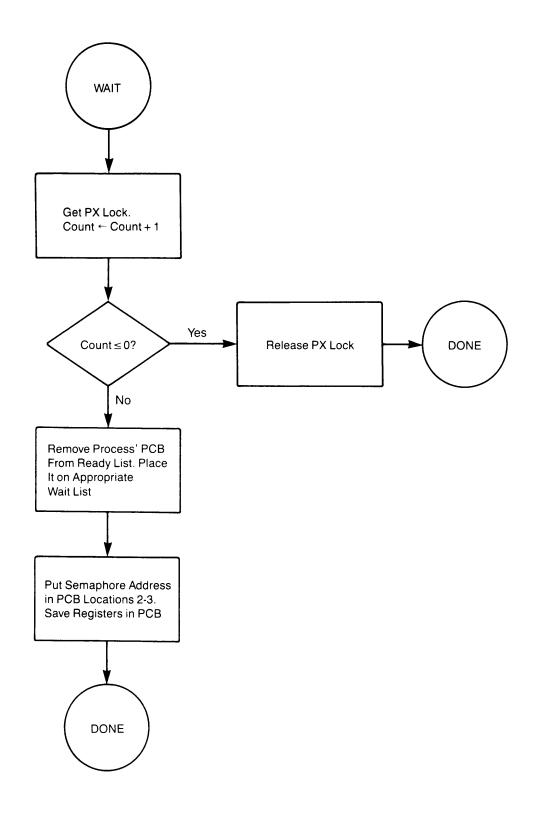

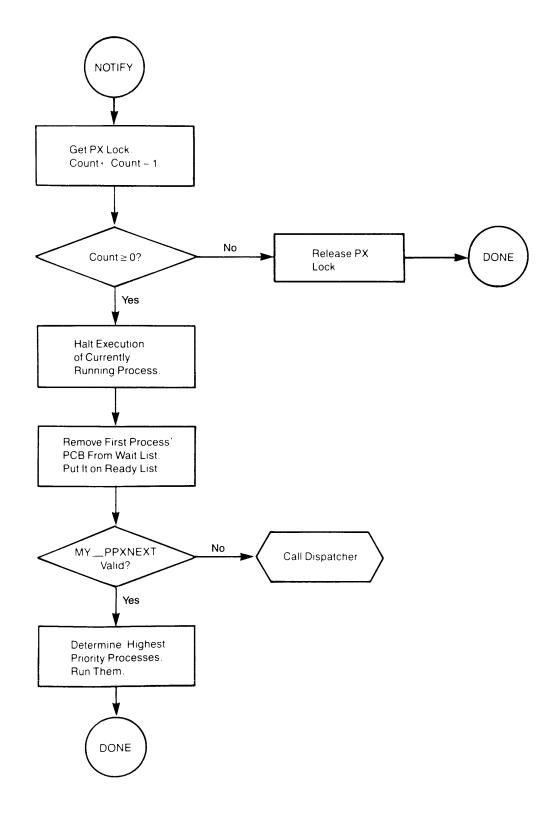

PRIME and PRIMOS are registered trademarks of Prime Computer, Inc. DISCOVER, INFO/BASIC, INFORM, MIDAS, MIDASPLUS, PERFORM, Prime INFORMATION, PRIME/SNA, PRIMELINK, PRIMENET, PRIMEWAY, PRIMIX, PRISAM, PST 100, PT25, PT45, PT65, PT200, PW153, PW200, PW250, RINGNET, SIMPLE, 50 Series, 400, 750, 850, 2250, 2350, 2450, 2550, 2650, 2655, 2755, 9650, 9655, 9750, 9755, 9950, 9955, and 9955II are trademarks of Prime Computer, Inc.

#### PRINTING HISTORY

First Edition (DOC9473-1LA) January 1985 Update 1 (UPD9473-11A) October 1985 Update 2 (UPD9473-12A) February 1986 Update 3 (UPD9473-13A) April 1986 Second Edition (DOC9473-2LA) August 1987

CREDITS

Editorial: Thelma Henner Project Support: The CPU Group Illustration: Mingling Chang and Anna Spoerri Document Preparation: Mary Mixon and Kathy Normington Production: Judy Gordon

# HOW TO ORDER TECHNICAL DOCUMENTS

To order copies of documents, or to obtain a catalog and price list:

#### United States Customers

# International

Call Prime Telemarketing, toll free, at 1-800-343-2533, Monday through Friday, 8:30 a.m. to 5:00 p.m. (EST).

Contact your local Prime subsidiary or distributor.

# CUSTOMER SUPPORT

Prime provides the following toll-free numbers for customers in the United States needing service:

| 1-800-322-2838 | (within Massachusetts) | 1-800-541-8888 | (within Alaska) |

|----------------|------------------------|----------------|-----------------|

| 1-800-343-2320 | (within other states)  | 1-800-651-1313 | (within Hawaii) |

For other locations, contact your Prime representative.

# SURVEYS AND CORRESPONDENCE

Please comment on this manual using the Reader Response Form provided in the back of this book. Address any additional comments on this or other Prime documents to:

Technical Publications Department Prime Computer, Inc. 500 Old Connecticut Path Framingham, MA 01701

# Contents

|   | ABOUT THIS BOOK                                                                                                                                                               | ix                                                       |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 1 | SYSTEM OVERVIEW                                                                                                                                                               |                                                          |

|   | Single-stream Architecture<br>Instruction Pipeline Use<br>Special Features of the 6350                                                                                        | 1-2<br>1-7<br>1-10                                       |

| 2 | PHYSICAL AND VIRTUAL MEMORY                                                                                                                                                   |                                                          |

|   | Physical Memory<br>Virtual Memory<br>Summary                                                                                                                                  | 2-2<br>2-5<br>2-8                                        |

| 3 | ADDRESSING                                                                                                                                                                    |                                                          |

|   | Units<br>Components of a Virtual Address<br>Components of an Instruction<br>Forming an Address<br>Addressing Modes<br>Summary of Addressing Modes<br>Address Traps<br>Summary | 3-1<br>3-2<br>3-5<br>3-8<br>3-10<br>3-12<br>3-31<br>3-35 |

| 4 | MEMORY MANAGEMENT                                                                                                                                                             |                                                          |

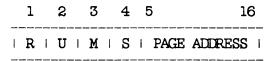

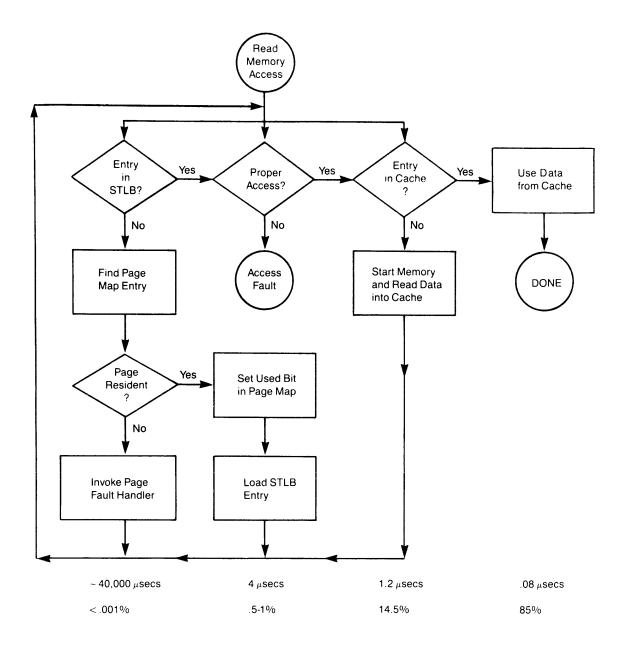

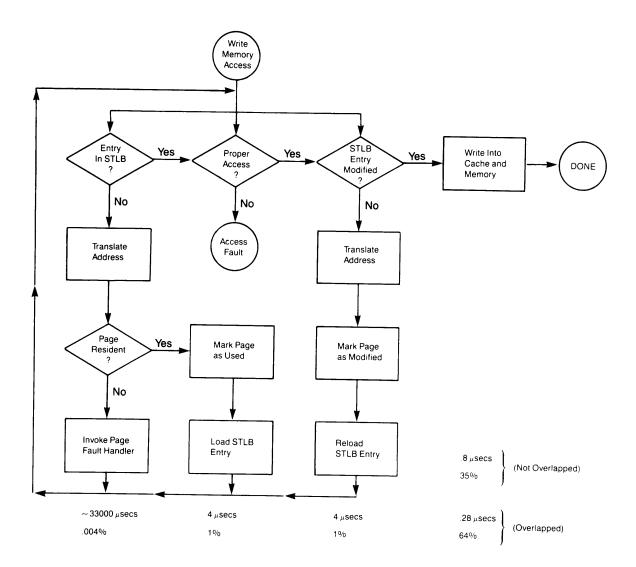

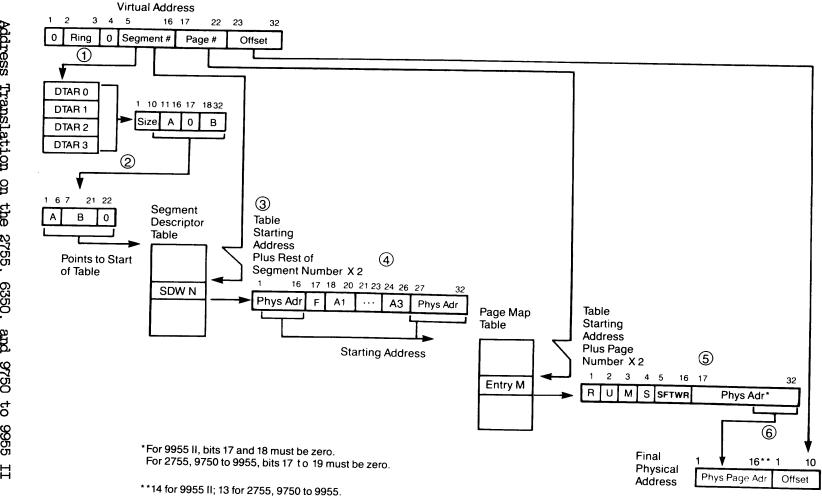

|   | The Virtual Address<br>Memory Management Data Structures<br>Accessing the STLB and Cache<br>Address Translation<br>Summary                                                    | 4-1<br>4-3<br>4-19<br>4-26<br>4-31                       |

| 5 | CONTROL INFORMATION AND RESTRICTED<br>INSTRUCTIONS                                                                                                                            |                                                          |

|   | Other System Data Structures<br>Restricted Instructions<br>Summary                                                                                                            | 5-1<br>5-11<br>5-12                                      |

# 6 DATATYPES

|    | Fixed-point Data<br>Floating-point Numbers<br>Decimal Data<br>Character Strings<br>Queues<br>Summary of Datatypes and                                                                                                           | 6-1<br>6-19<br>6-32<br>6-38<br>6-41<br>6-46                                     |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

|    | Applicable Instructions<br>Summary                                                                                                                                                                                              | 6-51                                                                            |

| 7  | ALTERING SEQUENTIAL FLOW                                                                                                                                                                                                        |                                                                                 |

|    | Branch and Skip Instructions<br>Jump Instructions<br>Summary                                                                                                                                                                    | 7-1<br>7-6<br>7-7                                                               |

| 8  | STACKS AND PROCEDURE CALLS                                                                                                                                                                                                      |                                                                                 |

|    | Definition of Terms<br>Stacks and Stack Management<br>Entry Control Blocks<br>Indirect Pointers<br>Gate Access<br>Making a Procedure Call<br>The ARGT Instruction<br>The PRTN Instruction<br>Programming Notes                  | 8-1<br>8-2<br>8-5<br>8-6<br>8-7<br>8-7<br>8-7<br>8-14<br>8-15<br>8-15           |

| 9  | PROCESS EXCHANGE                                                                                                                                                                                                                |                                                                                 |

|    | Introduction<br>Elements of the PXM<br>Process Control Blocks<br>Ready List<br>Wait Lists<br>PXM Instructions<br>Dispatcher<br>Register Files<br>Process Interval Timer<br>Dispatcher Operation<br>Fetch Cycle Traps<br>Summary | 9-1<br>9-2<br>9-2<br>9-7<br>9-9<br>9-16<br>9-16<br>9-25<br>9-27<br>9-30<br>9-30 |

| 10 | INTERRUPTS, FAULTS, CHECKS, AND TRAPS                                                                                                                                                                                           |                                                                                 |

|    | Breaks<br>Interrupts<br>Faults<br>Checks<br>Traps<br>Interval Clock<br>Summary                                                                                                                                                  | $10-1 \\ 10-3 \\ 10-6 \\ 10-18 \\ 10-37 \\ 10-46 \\ 10-47 $                     |

Summary

# 11 INPUT-OUTPUT

| Programmed I/O        | 11-2  |

|-----------------------|-------|

| DMx                   | 11–10 |

| DMA                   | 11–16 |

| DMC                   | 11–19 |

| DMT                   | 11-20 |

| DMQ                   | 11-21 |

| DMx Address Formation | 11-21 |

# APPENDIXES

| A | POWER-UP                                                                                                     | A-1                      |

|---|--------------------------------------------------------------------------------------------------------------|--------------------------|

| В | EARLIER PROCESSORS                                                                                           | B-1                      |

|   | System Overview<br>Physical and Virtual Memory<br>Addressing<br>Memory Management<br>Control Information and | B-2<br>B-5<br>B-6<br>B-8 |

|   | Restricted Instructions                                                                                      | B-11                     |

|   | Data Types                                                                                                   | B-11                     |

|   | Altering Sequential Flow                                                                                     | B-16                     |

|   | Stacks and Procedure Calls                                                                                   | B-17<br>B-17             |

|   | Process Exchange<br>Interrupts, Checks, Faults,                                                              | D-11                     |

|   | and Traps                                                                                                    | B-19                     |

|   | Input-Output                                                                                                 | B-27                     |

|   |                                                                                                              |                          |

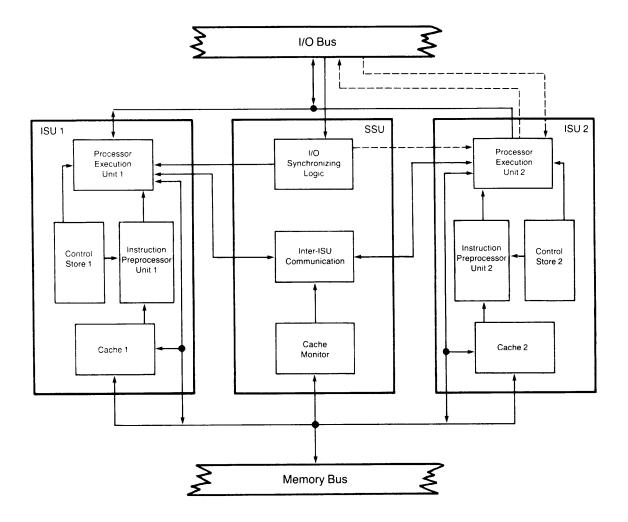

| С | PROCESS EXCHANCE ON THE 850                                                                                  | C-1                      |

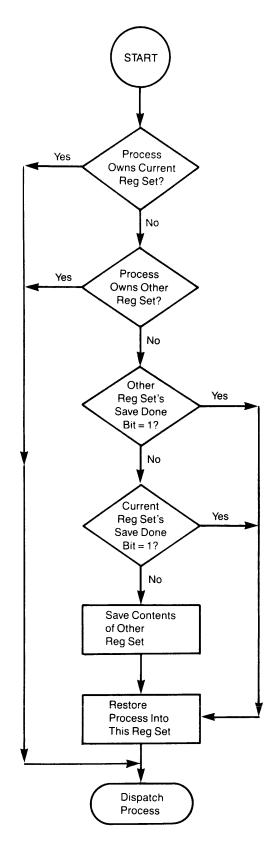

|   | Instruction Stream Units<br>850 Process Exchange Elements<br>Dispatcher Operation                            | C-1<br>C-2<br>C-11       |

| D | INSTRUCTION SUMMARY CHARTS                                                                                   | D-1                      |

| E | 2455 ARCHITECTURE                                                                                            | E-1                      |

|   | INDEX                                                                                                        | X-1                      |

# About This Book

Prime's 50 Series™family is a sophisticated group of totally compatible supermini computers. Its members are the Prime:

| 6350™        | 9955 II™       | 9955 <sup>™</sup> | 9950™ |

|--------------|----------------|-------------------|-------|

| 9755™        | 9750™          | 9655™             | 9650™ |

| 2755™        | 2655™          | 2550™             | 2450™ |

| 2350™        | 2250™          | 850™              | 750™  |

| 650™         | 550-II™        | 550 <sup>™</sup>  | 500™  |

| <b>4</b> 50™ | I <b>4</b> 50™ | <b>400™</b>       | 350™  |

| 250-II™      | 250™           | 150™              |       |

The 50 Series systems embody an advanced 32-bit architecture that grants the user the ability to perform complex tasks efficiently and quickly. This document describes the 50 Series architecture from a functional point of view.

#### NOTES TO THE READER

Groups of people will find this document useful: engineers, programmers, designers, and technicians. To read this book, you should have a basic understanding of computers, but not necessarily of Prime computers. Prime stresses a high degree of compatibility across its product line; therefore, you can apply much of the information contained in this book to other Prime machines, as well as to the 50 Series machines.

# ORGANIZATION OF THIS GUIDE

Because this guide stresses the functional aspects of the 50 Series processors, the topics are organized according to function. Chapter 1 presents a general overview. Chapters 2 through 11 each describe one aspect of the system, beginning with memory configuration and addressing and ending with the I/O system. Each chapter builds on the information contained in the previous one. Chapters 1 through 11 may be summarized as follows:

- Chapter 1 gives an overview of the 50 Series systems.

- Chapter 2 presents the configuration of the 50 Series physical and virtual memory.

- Chapter 3 discusses virtual addressing, modes and formats, and address traps.

- Chapter 4 describes memory management and its data structures.

- Chapter 5 gives the control data structures and restricted instructions.

- Chapter 6 specifies the datatypes supported on the 50 Series systems.

- Chapter 7 presents the branch, skip, and jump instructions.

- Chapter 8 defines procedure calls, the stack, and argument transfers.

- Chapter 9 describes single-stream process exchange and its data structures.

- Chapter 10 deals with interrupts, faults, checks, and traps.

- Chapter 11 discusses the I/O system (DMA, DMC, DMT, and DMQ).

Throughout these chapters are lists of Prime assembly language instructions that pertain to the topics under discussion. These lists briefly define the instructions' actions and show how they relate to the topics. Appendix A discusses system power-up and the initialization of registers.

Appendix B presents the characteristics of the following earlier processors: 2250, 850, 750, 650, 550-II, 450/550, 500, I450, 400, 350, 250-II, 250, and 150.

Appendix C describes process exchange on the 850, a processor with dual-stream architecture.

Appendix D contains instruction summaries for all modes.

Appendix E describes the system architecture for the 2455.

# PRIME DOCUMENTATION CONVENTIONS

The following conventions are used in command formats, statement formats, and in examples throughout this document. Examples illustrate the uses of these commands and statements in typical applications.

| Convention | Explanation                                                                                                                                    | Example     |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| UPPERCASE  | In command formats, words<br>in uppercase indicate the<br>names of commands, options,<br>statements, and keywords.<br>Enter them in uppercase. | CRL         |

| lowercase  | In command formats, words<br>in lowercase indicate vari-<br>ables for which you must<br>substitute a suitable value.                           | LDA address |

| Apostrophe | An apostrophe preceding a number indicates that the number is in octal.                                                                        | '200        |

# 1 System Overview

The CPUs of all 50 Series systems share a common architecture and one operating system. This commonality is what makes the 50 Series a line of completely upward-compatible and downward-compatible systems. The implementation of the common architecture, however, is slightly different for each member, allowing the 50 Series systems to address a wide variety of user needs as well as to remain compatible. The first part of this chapter explores the single-stream CPU implemented on the 2350 to 9955 II. The second part of this chapter discusses special features of the 6350, the newest processor.

#### Note

The earlier processors 2250, 750, 650, 550-II, 550, 500, 450, I450, 400, 350, 250-II, 250, and 150 are also single-stream CPU processors. This chapter identifies where their single-stream implementation differs from the current processors. For a detailed discussion of these differences, refer to Appendix B. The 850, another earlier processor, is the only system with a dual-stream architecture that is discussed in Appendix B also.

# SINGLE-STREAM ARCHITECTURE

The CPU can be divided into four major units. The first three of these are implemented on all single-stream members of the 50 Series family:

- Cache, STLB, and IOTLB

- Control store

- Execution unit

- Instruction unit

The instruction unit is a feature of the systems and serves as a mechanism to process instructions at a greater speed. Of the earlier processors, only the 750 and 850 have a fourth unit also, called the Instruction Preprocessor Unit and discussed in Appendix B.

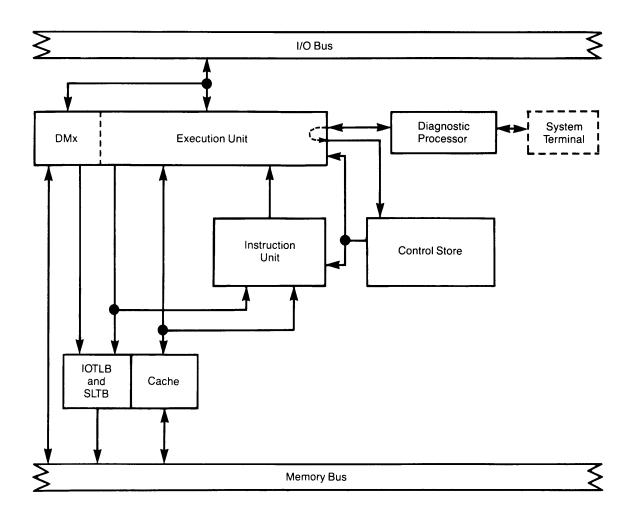

Figure 1-1 diagrams this architecture. This figure also shows the diagnostic processor which, among other functions, can load the control store and operate as the system terminal. The diagnostic processor also provides support for environmental sensors and the uninterruptable power supply. For the 6350, the diagnostic processor supports battery backup capability.

# Cache, STLB, and IOTLB

The 50 Series uses a virtually addressed, write-through <u>cache</u>. Each cache entry contains the contents of 32 bits of recently accessed physical memory. Each entry also contains parity and valid bits as well as the physical page number that contains the 32 bits. (For the cache entry format on the earlier processors, see Appendix A.)

The 6350 has a two-set associative cache that is accessed in parallel to return two cache entries, each for the contents of 32 bits. Thus, two virtual addresses with the same cache index address can be used together without references to the one virtual address forcing the data for the other virtual address to be overwritten. This effectively eliminates two-way thrashing that could reduce performance.

If the contents of a specified location can be found in the cache, the system saves a great deal of time: it takes only 0.25 to 0.5 of the minimum instruction time to access the cache and get a cache hit, a vast improvement over the approximately 2 to 6 times the minimum instruction time needed to access physical memory. The time saved can be spent performing other operations rather than waiting for a memory reference to complete.

Block Diagram of Single-processor Architecture Figure 1-1 To speed up the virtual to physical address translation, the <u>STLB</u> (Segmentation Table Lookaside Buffer) contains the results of the last translations: 1024 translations on the 6350; 512 translations on the 2350 to 2755, 9650, and 9655; and 128 translations on the 9750 to 9950.

The 6350 has a two-set associative STLB that is accessed in parallel to return two STLB entries. Thus, two virtual addresses with the same STLB entry address can be used together without references to the one forcing the mapping for the other virtual address to be overwritten. This effectively eliminates two-way thrashing that could reduce performance.

Because programs tend to reference the same set of locations during their execution, the system can perform a translation once, store the result in the STLB, and then have it for reference the next time the user specifies the same location. Because the STLB has a much faster access time than physical memory does, referencing it saves translation time as well as access time.

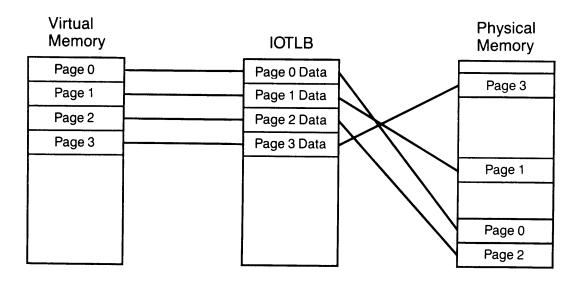

Mapped I/O allows the limited addressing range of DMx input/output transfers to address all of physical memory. It is especially useful when the processor is transferring several contiguous pages in virtual memory to physical locations that may not be contiguous. The <u>IOTLB</u> contains the information needed to map the transfer addresses to physical memory locations. The IOTLB, with the STLB, forms the virtual-to-physical address mapping hardware and contains 256 entries for the 6350, and 128 entries for the 2350 to 2755, 9650 to 9955 II.

See Chapter 4, MEMORY MANAGEMENT, for more information about cache, STLB, and address translation. See Chapter 11, INPUT-OUTPUT, for a description of the IOTLB.

#### The Control Store Unit

To speed up execution, the 50 Series systems implement many functions, such as procedure calls, in hardware and firmware. (Procedure calls are explained in Chapter 8.) The firmware that governs instruction execution is contained in the control store RAM: 80 Kbytes for the 6350; 50 Kbytes for the 9750 to 9955 II; 128 Kbytes for the 2755; and 64 Kbytes for the 2350 to 2655, 9650, and 9655.

# The Execution Unit

This unit performs the computation required during instruction execution. Elements of the processor execution unit include:

- Integer arithmetic logic unit (ALU)

- Decimal ALU

- Floating point unit

- Register file

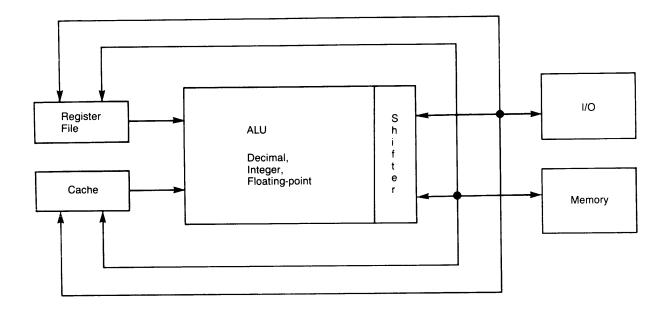

Figure 1-2 shows a diagram of the processor execution unit.

ALUS: The integer arithmetic logic unit (ALU) performs the desired operation on the user's two's complement data. In a similar fashion, the decimal ALU and the floating-point unit handle decimal and floating-point operations, respectively. These units can perform tests and checks as well as arithmetic operations.

Register File: The register file contains up to eleven sets of registers, depending on the processor model. Each set contains 32 32-bit registers. There are three types of register sets: user, microcode scratch and system status, and DMA. User register sets contain information about a process and about the system as the process sees it. Specifically, user register sets contain information about the general registers a process can use, addresses of fault handlers, contents of system registers, and other useful information.

Direct memory registers contain direct memory access (DMA) channels to speed I/O operations as discussed in Chapter 11.

The 6350 and 9750 to 9955 II have eight register sets: four sets of user registers, two sets of microcode scratch and system status registers, one set of direct memory access registers, and one reserved.

The 2350 to 2755, 9650, and 9655 have eleven register sets: eight sets of user registers, three sets of microcode scratch and system status registers, and one set of direct memory access registers.

See Appendix B for the registers sets of the earlier processors listed on page 1-1.

Execution Unit Figure 1-2

# The Instruction Unit

The 2350 to 9955 II have an instruction unit designed to speed up execution by processing information about instructions before execution. The instructions are read from cache and decoded to provide the information necessary for effective address formation and for execution of the instruction.

# INSTRUCTION PIPELINE USE

The 2350 to 9955 II use a pipeline to speed up instruction decoding and execution. The pipeline of the 6350 and 9750 to 9955 II has five stages. The pipeline of the 2350 to 2755, 9650, and 9655 has two phases. Both pipelines are discussed below.

# The Five-Stage Pipeline

The 6350 and 9750 to 9955 II use a five-stage pipeline technique for executing instructions in parallel, thus speeding up instruction execution considerably. The execution of each instruction for this pipeline through the five stages is shown in Table 1-1. Each stage takes two beats to complete, where a beat is a certain constant of time. The <u>beat rate</u> is the minimal time interval that the processor requires to perform some useful task.

A processor using the five-stage pipeline executes instructions in parallel. This means that the processor does not have to complete the entire five-stage sequence for one instruction before it can begin executing the next. Rather, instructions are processed somewhat like cars in a factory assembly line. The cars travel past a number of specialized stations. At each station a specific operation takes place. Then the car moves on. After a certain length of time the next car arrives at the same station where the same operation occurs.

The five-stage pipeline processes instructions in a similar fashion. After every other beat, a new instruction arrives at a station, and that station's operation is performed on it.

Using the pipeline in this fashion, a processor executes Stage 1 of the first instruction. When it begins on Stage 2 (Beat 3) of the first instruction, that processor can also begin Stage 1 (Beat 1) of the second instruction. Likewise, when a processor begins Stage 2 (Beat 3) of the second instruction, it can also begin Stage 1 (Beat 1) of the third, and so on. This means that the pipeline can begin a new instruction every other beat.

| Stage       | Beat           | Action                                                                                                                                 |

|-------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------|

|             | 1              | Send the contents of the lookahead program I register to the memory address register.                                                  |

| 1           | 2              | Read the next instruction from the cache.                                                                                              |

| 2           | 3  <br>        | Start decoding the address of the next instruction.                                                                                    |

| 2           | <u>4</u>  <br> | Read the contents of the base and index registers.                                                                                     |

| <br>  3<br> | 5  <br>  1     | Form the effective address and the control                                                                                             |

| 3           |                | Send the contents of the effective address<br>register to the memory address register and<br>fetch the contents of the next microword. |

| <br>  4<br> | 7  <br>        | Read the operand from the cache and register  <br>file.                                                                                |

| 4           | <br>           | Execution, phase 1 (ALU).                                                                                                              |

| 15          | 9  <br>  9     | Execution, phase 2. (Transfer results to RS.)                                                                                          |

| 1 5         | 1 10 1         | Store the results of the operation.                                                                                                    |

Table 1-1 The Five-Stage Instruction Pipeline

The rate of instruction-flow through the pipeline is determined by the processor's use of system elements at each beat. As shown in Table 1-1, Beats 2 and 7 both use the cache, and Beats 7 and 10 both use the register file. When two instructions in the pipeline request the same element at the same time, a conflict occurs. Starting a new instruction every other beat minimizes this type of conflict.

When there are no conflicts in the pipeline, simple instructions complete execution every two beats. Some instructions, however, require more than two beats to complete execution. When this occurs, the pipeline holds up operations on the subsequent instructions until it has completed the extra operation for the first instruction. During the holdup, the processor still forms control store addresses and fetches microcode words, but it performs no prefetch or effective address calculations. The Branch Cache and the Five-Stage Pipeline: The 6350 and 9750 to 9955 II use a memory called the branch cache to record and predict the target address for jump and branch instructions. The branch cache contains 256 to 1024 entries, depending on the processor model.

Because these processors execute instructions in parallel in their pipeline, they might begin to execute instructions down an incorrect path, following a branch, before they had determined the correct branch address. If this occurs, the processor must flush the pipeline of all instructions from the wrong branch path, and then must begin execution down the correct branch path. This sequence of steps causes a delay.

To minimize the chance of such an occurrence, the branch cache contains information about the branches that have previously occurred in the program. The processor uses this information to determine which branch was most recently taken for each conditional instruction. The processor then assumes that the same branch will be taken this time. If the prediction is wrong, the processor adds a new entry in the cache, specifying the correct branch for future use.

Flushing the Five-Stage Pipeline: If an instruction stores data into the stream of instructions that follows it, the five-stage pipeline may have to be flushed before further calculations take place. Store-instructions in S and R modes automatically flush the pipeline; therefore, no further actions are required and performance is reduced substantially. V mode and I mode store instructions, however, do not automatically flush the pipe. Either an E64V (V mode) or an E32I (I mode) instruction will perform the flush.

Prime systems are designed for pure procedure. All translator-generated code avoids storing into the instruction stream.

# The Two-Phase Pipeline

The 2350 to 2755, 9650, and 9655 use a two-phase pipeline technique for decoding and executing instructions in parallel, thus speeding up instruction execution. While these processors perform the effective address formation and execution of one instruction, the next instruction is read from cache and decoded.

#### SPECIAL FEATURES OF THE 6350

Although the 6350 follows the general architecture of the 50 Series as shown in the previous discussions, it contains several features designed for outstanding performance in a multiuser environment.

#### Two-Set Associative STLB

The two-set associative STLB increases the likelihood that the physical translation of a virtual address is in the STLB. This lessens the chance that the slower virtual-to-physical address translation mechanism has to be used.

#### Two-Set Associative Cache

The two-set associative cache increases the probability that the cache will contain the correct data. This feature increases the likelihood that the physical translation of a virtual address is in the STLB. The combination of the two-set associative cache and the two-set associative STLB adds up to increased performance for the 6350.

#### 10KH ECL Design

For swift execution of instructions, the 6350 uses 10KH ECL (emitter coupled logic). Memory parts using 10KH ECL are about twice as fast as those made of ECL at the same power level. Most of the logic is contained in semi-custom gate arrays.

#### Barrel Shifter

To speed up floating-point operations, the 6350 uses a barrel shifter. Moreover, this feature provides more power for manipulations performed in shift and rotate instructions.

#### Expanded I/O System

The 6350's I/O system has been expanded to speed up I/O performance and permit the parallel operation of a greater number of controllers. This feature is achieved through the use of new DMx operations and four I/O segments (0 to 3).

The 6350's new DMx operations are extended DMA, 32-bit single transfer DMA, 32-bit burst mode DMA, and 16-bit burst DMT.

In extended DMA, theDMA control words can be located anywhere in the I/O segments in memory, not just in the DMA register file, as long as the control word is 32-bit aligned. Single 32-bit DMA transfers 32 bits at a time instead of 16, and 32-bit burst mode transfers four 32-bit quantities at a time rather than four 16-bit ones.

DMT has been expanded on the 6350 to allow 16-bit burst DMT, whereby the CPU receives a main memory address and then reads or writes four 16-bit quantities at a time rather than just one.

# Ambient Temperature Environmental Sensor

The 6350 now has an ambient temperature environmental sensor that detects when the air surrounding the processor has exceeded a certain temperature. Chapter 10 discusses this in further detail.

# Battery Backup Capability

In the event of a power failure, the 6350 has a battery backup capability that keeps powered the memories, maintenance processor, and memory refresh logic of the CPU.

# 2 Physical and Virtual Memory

The 50 Series processors are virtual memory systems. This means that a very large, protected, virtual address space is available to each user who is logged onto the system. This virtual address space is supported by a much smaller physical address space invisible to the user.

Virtual memory has several advantages. To the user logged onto the system, there appears to be an address space of almost unlimited size, which can support very large applications without using overlays. This address space is protected against unauthorized accesses in hardware. To the system owner, a virtual memory scheme provides the ease of use of a large memory at the cost of a much smaller amount of hardware.

The three key parts to a virtual memory scheme are <u>physical memory</u>, <u>virtual memory</u>, and a <u>manager</u> to control the virtual memory scheme. The manager is the operating system, PRIMOS, and its attendant hardware and firmware support. This chapter describes the characteristics of the 50 Series physical and virtual memory, and shows how PRIMOS coordinates the 50 Series virtual memory scheme. It also describes some of the hardware protection mechanisms implemented in the 50 Series virtual memory.

# PHYSICAL MEMORY

Physical memory encompasses all hardware parts of the system used to store large blocks of information. There are three types of physical memory:

- Cache

- Main memory

- Disk

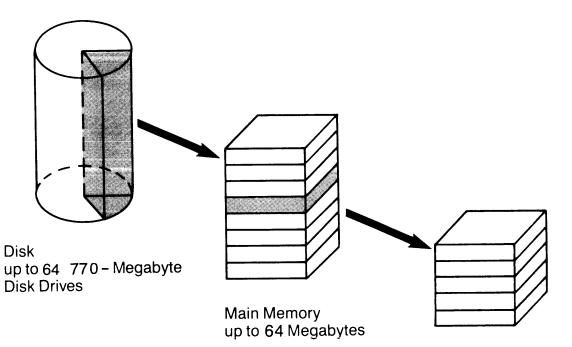

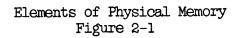

Figure 2-1 shows the relationship between the three elements of physical memory.

Cache up to 64 Kilobytes

# Cache

The cache is a data buffer that stores copies of the information contained in the most frequently referenced memory locations. Its size varies from system to system as shown in Table 2-1. During program execution, this buffer is used to speed up memory references.

Consider the following. Since cache is a form of very high speed memory, it takes only 0.25 to 0.5 of a minimum instruction time to access data stored there. In contrast, it takes about 2 to 5 times a minimum instruction time to access data stored in main memory. This difference in access times makes it very advantageous to access cache whenever possible.

Three factors determine how often the cache contains the correct data (known as the cache hit rate):

- The size of the cache (16 to 64 Kbytes)

- The organization of the cache (two-set associative or one-set)

- The information fetch rate (block size) of 32 to 64 bits, depending on the system and the amount of memory interleaving

- Locality of reference (the tendency of a program to execute within a small part of itself at any time)

The 50 Series cache hit rate varies from system to system. See Table 2-1 for details.

|      | System                           |   | No. Sets | 1         | Size Per Set |   | Total Size | 1 | Rate |            |

|------|----------------------------------|---|----------|-----------|--------------|---|------------|---|------|------------|

| <br> | 2350 to 2655 and<br>9650 to 9950 |   | 1        | 1         | 16 Kbytes    |   | 16 Kbytes  |   | 95%  | <br> <br>1 |

| 1    | 2755, 9955, and<br>9955 II       | 1 | 1        | <br> <br> | 64 Kbytes    | 1 | 64 Kbytes  | 1 | >98% |            |

| Ι    | 6350                             | I | 2        | I         | 16 Kbytes    | I | 32 Kbytes  | i | >98% | i          |

| Table 2-1 |       |     |     |        |

|-----------|-------|-----|-----|--------|

| Cache     | Sizes | and | Hit | Rates* |

\*For earlier systems (listed on page 1-1), see Appendix B.

#### Main Memory

Packaged onto printed circuit boards, the main memory uses dynamic random access storage devices for data retention. All memory incorporates error detection and correction techniques and the capability of performing two-way interleaving.

Error detection and correction allows the memory to remain functional and to output correct data when a single bit in a 16-bit or 32-bit quantity (depending on processor model) has become faulty. This type of error is referred to as an ECCC. If more than a single bit in a single 16-bit quantity is in error, the fault is uncorrectable, an ECCU. All two-bit errors are detected as well as many multi-bit errors.

Interleaving effectively decreases the memory cycle time, increases memory accessibility, and allows more efficient use of the I/O bus.

There are two types of memory for all 50 series processors: the array card driven by a memory controller for the 6350 and 9750 to 9955 II; and the standalone memory subsystem for all other 50 Series processors.

The memory array cards used on the 6350 and 9750 to 9955 II require a memory control unit to supply commands, error detection and correction, and all interaction to and from the central processing unit. The 8-megabyte board has a 64-bit-wide storage capability that interacts directly with the memory bus. The total main memory capacity of the 6350 and 9750 to 9955 II is as follows.

| 9750 and 9755: | 12 megabytes |

|----------------|--------------|

| 9950 and 9955: | 16 megabytes |

| 9955 II:       | 32 megabytes |

| 6350:          | 64 megabytes |

Each standalone memory board used by the 2350 to 2755, 9650, and 9655 has a memory capacity of 2 or 4 megabytes to provide a maximum storage capacity as follows:

| 2350 to 2655:  | 8 megabytes  |

|----------------|--------------|

| 9650 and 9655: | 8 megabytes  |

| 2755:          | 16 megabytes |

The board itself has a 32-bit-wide storage capability that interacts directly with the memory bus.

Appendix B contains a description of the standalone memory subsystem for the earlier processors listed on page 1-1.

Disk

Disks provide storage for all virtual memory. With the proper access rights, the system or user can access this information. When the disk is accessed, a copy of the information is moved from disk to main memory.

# VIRTUAL MEMORY

Virtual memory is divided into units called <u>segments</u> that contain up to 128 Kbytes each. Segments are virtual units, not physical ones, that aid the user and the system in organizing their virtual address spaces. For example, the user can organize program code in one segment and program data in a second one. Segments make it possible to allow extra room in a program for variable length data structures, such as arrays whose dimensions can change each time the program runs. Segments also allow the user to build modular programs, one module to a segment. PRIMOS uses segments similarly to organize its own code into modules.

The virtual address space of each user contains 4096 segments. These are subdivided into four groups of 1024 segments each. The segments are subdivided to make address translation and segment sharing easier. (See the next section and Chapter 4, MEMORY MANAGEMENT.)

# Shared and Unshared Segments

In the Prime virtual memory scheme (diagrammed in Figure 2-2), each user address space of 4096 segments is divided into shared and unshared space. The first 2048 segments are shared with all other users. This allows the operating system, shared libraries, and shared subsystems to be seen by all users. This means that if two users reference segment 2000, they are specifying the same location.

The second 2048 segments are private, containing information unique to each user. This means that if two users reference segment 4000, they are specifying completely different locations.

This arrangement of shared and unshared segments means that there is no possibility of one user's private space conflicting with that of another user. It also means that only one copy of PRIMOS and the shared system software need be maintained, and thus reduces memory use. Moreover, it means that PRIMOS is embedded in the virtual address space of each user and is directly accessible via a normal procedure call. (See Chapter 8, STACKS AND PROCEDURE CALLS.) No interrupts, special supervisor calls, or system traps are necessary when the user accesses PRIMOS or any utility, library, or subsystem residing in shared space.

50 Series Virtual Memory Space Figure 2-2

# Protection Rings

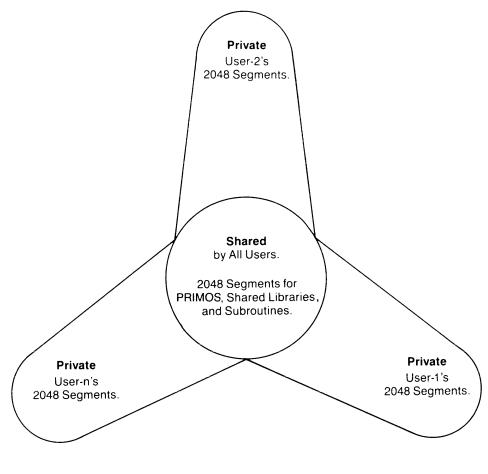

Designating shared and unshared segments is not the only form of protection available to the 50 Series virtual memory. Three hardware implemented rings provide a simple, unbreakable form of security that checks each memory reference for its right to access the specified part of memory.

The rings represent levels of privilege, and are diagrammed in Figure 2-3. All executing procedures run with a given ring number. This ring value represents the rights, or privilege, of access in virtual memory. A process running under Ring 3 has the most restrictions, while a process running under Ring 0 has no restrictions.

Code that is executed under Ring O privilege must also have the greatest protection to prevent accidental or intentional misuse. The protection rings serve to provide this kind of protection so that a Ring 3 program is restricted from reading, writing, and/or executing Ring O data or code. Access is only provided to Ring O operating system routines through the use of special gates set up for that purpose.

Protection Rings Figure 2-3

A Ring 3 program can therefore make a gated call to a Ring 0 routine. This is referred to as an inward call. Procedures that require greater access than is provided under Ring 3, but not as much as granted under Ring 0, operate under Ring 1 protection. Ring 1 procedures can also perform inward calls to Ring 0 procedures. See Chapter 8 for more information on procedure calls and gates.

See Chapter 4, MEMORY MANAGEMENT, for information about how rings govern the virtual-to-physical address translation to prevent invalid accesses.

# Segmentation Table Lookaside Buffer

Virtual memory has its counterpart of the cache, the <u>STLB</u>. The system uses this buffer with the cache to reduce the time needed to access information. Where a cache entry contains information about a recently accessed physical memory location, an STLB entry contains the information the system needs to find the physical location from the virtual address the user specified. Each entry also specifies the protection attributes associated with the location. Chapter 4 describes more about how the STLB is used.

# SUMMARY

This chapter describes the configuration of the 50 Series physical and virtual memories. Chapter 3, ADDRESSING, shows how to form a virtual address that references a location within the virtual address space. Chapter 4, MEMORY MANAGEMENT, shows how the 50 Series systems use the virtual address and the virtual-to-physical address translation process to integrate virtual and physical memory.

# **3** Addressing

The 50 Series processors support several kinds of addressing: direct addressing, indexed addressing, indirect addressing, indirect indexed addressing, and general register relative (GRR) addressing (unavailable for the earlier processors listed on page 1-1). They also support several modes of addressing, each with its own uses and benefits. This chapter:

- Provides an overview of virtual addressing and of effective address calculation.

- Explains how effective address calculation is done for each type of addressing, and what registers are involved.

- Explains the various modes of addressing.

- Provides summaries of instruction forms for each type of addressing in each mode.

# UNITS

The basic units of information are bits, bytes, halfwords, and words. A byte contains eight bits. One halfword contains two bytes; the bits are labelled from 1 (most significant bit) to 16 (least significant bit). A word contains four bytes. The bits are labelled from 1 to 32.

Memory is measured in bytes. The 50 Series physical memory size can be up to 64 Mbytes; the virtual address space contains 512 Mbytes.

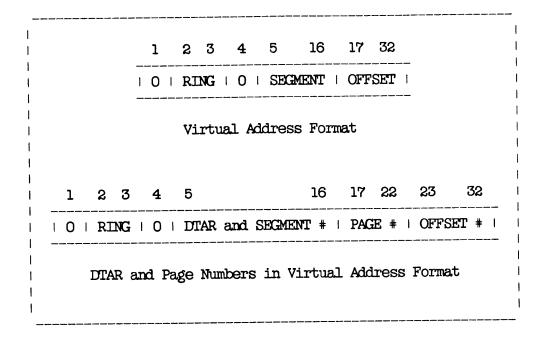

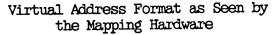

# COMPONENTS OF A VIRTUAL ADDRESS

A virtual address refers to a unique location in a user's virtual address space. The location is characterized by three elements: a ring number, a segment number, and an offset within that segment. (All offsets are relative to the first location within a segment, and are expressed in units of halfwords.) The format of a virtual address is shown in Figure 3-1.

When an instruction makes a memory reference, it provides information from which the virtual address can be calculated. This is frequently referred to as calculating the <u>effective</u> address. Depending on the type of instruction, the information can be provided in several different formats, and the calculation done in various ways. This section explains the various ways in which the ring number, segment number, and offset can be specified. It also explains the use of the indirect bit. The section Forming an Address explains how each of the four types of addressing uses these components to calculate the effective address.

# Ring Number

<u>Ring numbers</u> are found in the program counter, in the base register, within indirect addresses, and also in data blocks such as ECBs. When an effective address is calculated, the highest numbered ring referenced in any of these locations is chosen as the ring field for the effective address. (For more information on rings, and on the process of calculating ring numbers, see Chapter 4.)

#### Segment Number

The segment number is generally provided in one of four ways:

- If the instruction contains a base register field, the segment number is found in the specified base register.

- If the instruction does not contain a base register field, the segment number is found in the program counter.

- In indirect addressing, the <u>segment number field</u> contains the segment number.

- In I mode general register relative (GRR), bits 5 to 16 of the specified source register contain the segment number. (GRR is unavailable for the earlier processors listed on page 1-1.)

Base Registers: Four 32-bit base registers are available for use in address calculation:

- The procedure base register (PB)

- The stack base register (SB)

- The link base register (LB)

- The auxiliary base register (XB)

The format of these registers is shown in Figure 3-1.

| 1   | 23    | 4 | 5       | 16 17 |        | 32 |

|-----|-------|---|---------|-------|--------|----|

| I C | IRING | 0 | I SEGME | NT I  | OFFSET |    |

| Bits            | Name                | Description                                                                                                                                             |

|-----------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | <br> <br> <br> <br> | Must be 0. (See the F bit in<br>the section on <u>Calculating</u><br><u>Indirect Pointers</u> , in<br>Chapter 8, for the<br>explanation of this.)       |

| 2 to 3          | ' Ring              | Specifies the ring number.                                                                                                                              |

| 4<br> <br> <br> | <br> <br> <br>      | Must be 0. (See the E bit in 1<br>the section on <u>Calculating</u><br><u>Indirect Pointers</u> , in 1<br>Chapter 8, for the 1<br>explanation of this.) |

| 5 to 16         | Segment             | Specifies the segment number.                                                                                                                           |

| 17 to 32        | Offset              | Specifies the offset value.                                                                                                                             |

Format of Virtual Addresses and Base Registers Figure 3-1

The PB contains the address of the currently active procedure. It is unique among the four base registers because its offset is always O. The program counter always contains a trusted copy of the segment number in the PB. Therefore, an instruction that contains no base register field uses the same segment number as one that specifies the PB.

SB contains the starting address of the stack for the currently active stack frame. LB contains the starting address of a save area for static variables, such as an entry control block. Because short instructions reference LB-based variables starting from '400, the value loaded into LB is usually '400 less than the start of the save area. References then add an extra '400 to their displacement. (See Chapter 8.) XB usually contains a temporary pointer, such as that to a FORTRAN common block. These three registers usually have nonzero offsets. Thus, they supply not only the segment number but also an offset address relative to that number.

# Offset

The offset portion of an effective address is supplied by one or more of the following components:

- <u>Displacement</u>: a 16-bit number given explicitly within the instruction. In S, R, and V modes, the displacement can be 9 bits of the instruction that is added to or concatenated with the program counter.

- <u>Base register</u>: if the base register is SB, LB, or XB, it will contain an offset to be added to the displacement given within the instruction.

- <u>Index register</u>: if an index register is used, then the contents of that index register are to be added to whatever other offset has been calculated. When an I mode general register is used as an index register, only the contents of bits 1 to 16 are added to the offset.

- Indirect address: if indirect addressing is used, the indirect address contains the offset. Short form offsets are 16 bits. Long forms are 20 bits (bit pointers). Short form C language pointers are 17-bit offsets (byte pointers). (C language pointers are not available for the earlier processors listed on page 1-1.)

- Source register: if general register relative (GRR) is used, bits 17 to 32 of the source register will normally contain the offset. This is interpreted as the following C language pointer bits: the contents of bits 17 to 32 concatenated with the content of bit 4. (GRR is not available for the earlier processors listed on page 1-1.)

In summary, an offset can be calculated in any of the following ways:

- Displacement

- Displacement + offset from BR

- Displacement + index register (or source register low for GRR)

- Displacement + offset from BR + index register

- Indirect address

- Indirect address + index register

The instruction format tells the processor which method to use.

# COMPONENTS OF AN INSTRUCTION

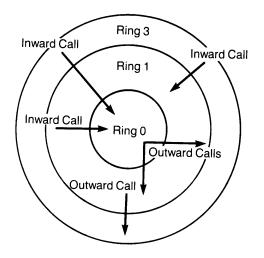

# Instruction Format

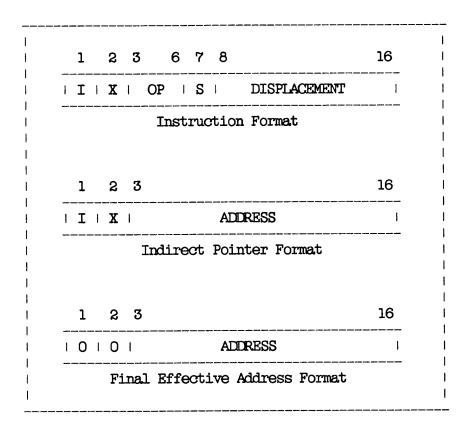

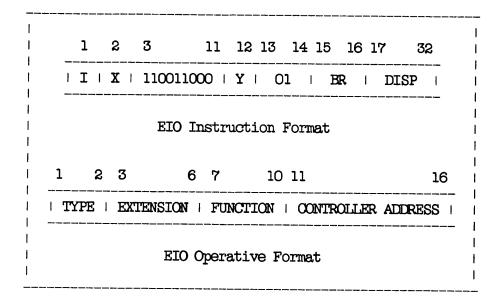

Figure 3-2 diagrams a typical instruction format. Thus, it shows how all the fields described in this chapter fit together into a single instruction.

| נ |   | 2 | S | į | 3  | 6 | 7 | , |     | 1] | L | 12 | 3 | 13 | 14 | 15 | 5  | 16 | 17 |      | 32 |

|---|---|---|---|---|----|---|---|---|-----|----|---|----|---|----|----|----|----|----|----|------|----|

|   | I |   | X |   | OP |   |   | 1 | 100 | 0  | 1 | Y  |   | 01 |    |    | BR |    |    | DISP |    |

|   | Bits     |               | Mnem | 1    | Name          | Description                         |

|---|----------|---------------|------|------|---------------|-------------------------------------|

| - | 1        |               | I    | 1    | Indirect bit  | Specifies indirect addressing.      |

|   | 2        |               | X    |      | Index field   | Specifies use of an index register. |

| 1 | 3 to 6   | 1             | OP   |      | Opcode        | Specifies the operation to perform. |

| 1 | 7 to 11  | <br> <br>     |      | 1    |               | Specifies instruction format.       |

| 1 | 12       |               | Y    |      | Index field   | Specifies use of an index register. |

| 1 | 13 to 14 | י<br>:        | OP   | 1    | Opcode        | Specifies the operation to perform. |

| 1 | 15 to 16 | 1<br>5  <br>1 | BR.  |      | Base register | Specifies the base register to use. |

|   | 17 to 32 | <br>          | DISP | <br> | Displacement  | Specifies a 16-bit offset.          |

Format of a Typical Instruction (V Mode, Long) Figure 3-2

The figure shown above explains the parts of a typical instruction. Instruction formats for all addressing modes, such as 64V short form or 32I, are provided later in this chapter.

#### Indirect Bit

An instruction may contain an <u>indirect bit</u>. If this bit is 1, it signifies that the address being calculated is an indirect address. If this bit is 0, the address is a direct address. (Indirect addresses are explained in the section Forming an Address, later in this chapter.)

# Index Register Field

An instruction may specify two index registers by using the  $\underline{X}$  and  $\underline{Y}$  fields. Each of these fields is one bit long. These fields are encoded with the contents of the I field to specify the type of indexing to be performed. (See Table 3-4 for the encoding.) If an index register is specified, then the contents of that index register are added to whatever other offset has been calculated.

# Base Register Field

The base register field of an instruction may contain one of the following four values:

Value Base Register

| 00 | PB (Procedure Base) |

|----|---------------------|

| 01 | SB (Stack Base)     |

| 10 | LB (Link Base)      |

| 11 | XB (Auxiliary Base) |

The value tells the processor which base register to check for the correct segment number (and, perhaps, offset).

# Displacement

The displacement field contains a 16-bit number representing an offset within a segment. As the section on <u>Offset</u> explained, the value given by the displacement may either stand alone or have other values added to it to provide the actual offset for the effective address.

# FORMING AN ADDRESS

The processor uses the contents of the fields in a memory reference instruction to select which of the four types of address formations to use:

- Direct

- Indexed

- Indirect

- Indirect indexed

- General register relative (for the 2350 to 9955 II only)

#### Direct Addressing

In direct addressing, the processor forms the effective address by adding the contents of the base register to the displacement.

# Indexed Addressing

The processor adds the contents of the base register, index register, and displacement to produce the effective address.

S, R, and V mode instructions that contain 1101 in bits 3 to 6 cannot specify indexing. See the tables at the end of this chapter for specific information.

# Indirect Addressing

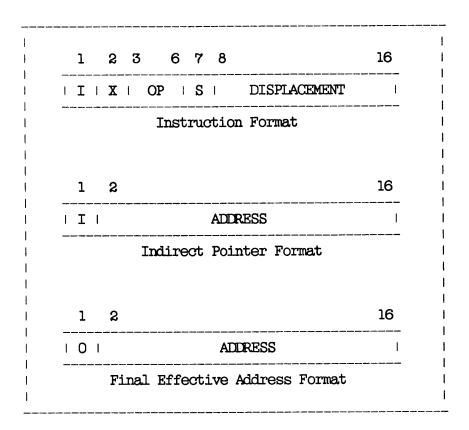

Short Form Indirection: Depending on the addressing mode, indirect addressing takes one of two forms. In the first, the processor treats the displacement as the address of a location in the procedure segment. The processor uses the contents of the addressed location as the effective address. This is called short form, or 16-bit, indirection.

Some addressing modes allow more than one level of indirection. (See the 16S, 32S, and 32R sections at the end of this chapter.) In these cases, the processor uses the displacement as the address of some location in the address space. If this addressed location contains another indirect address, then the processor uses these contents as the address of another location in memory. This <u>indirection chain</u> is followed until one addressed location does not contain an indirect address; these contents are called the <u>result of the chain</u>. The processor uses the result of the chain as the effective address. The tables at the end of this chapter specify the number of levels of indirection supported by each addressing mode.

Long Form Indirection: In long form indirect addressing, the instruction points to a location in memory that contains a 32-bit (or, more rarely, 48-bit) pointer. These long pointers contain not only addresses but also 2 or 3 fields that provide additional information.

Figure 3-3 shows the format of those pointers. The bits of special interest are the extension bit (or <u>E bit</u>), the <u>fault bit</u> (or <u>F bit</u>), and the <u>bit</u> number field.

The functions of these three fields are as follows:

- F bit If F = 1, a pointer fault is generated when this indirect address is used. (See Chapter 10 for information on pointer faults.)

- E bit If E = 0, the pointer is a 32-bit pointer. If E = 1, the pointer is a 48-bit pointer. (Throughout the rest of the chapter, discussions assume that the 32-bit format is being used.)

- Bit number Permits you to specify (or point to) a particular bit within an address offset.

|     | ـــــــــــــــــــــــــــــــــــــ | 2<br>  | 34     | : 5<br>         |                  | 16 17         |           | 32        |

|-----|---------------------------------------|--------|--------|-----------------|------------------|---------------|-----------|-----------|

|     | F                                     | RII    | ΓGΙΕ   | I S             | EGMENT           | T             | OFFSET    | 1         |

|     | Ind                                   | lirect | ; Poin | ter F<br>(E is  | ormat,<br>alway: | Long<br>s O.) | Form (32- | <br>-bit) |

| 1 : | 3                                     | 34     | 5      | 10              | 6 17             | 32            | 33 36 37  | 48        |

| F   | RING                                  | E      | I SEX  | MENT            | I OFFS           | SET I         | BIT#   RE | SERVED    |

|     | Ind                                   | irect  | Poin   | ter Fo<br>(E is | ormat,<br>always | Long          | Form (48- | bit)      |

Pointer Formats for Long Form Indirection Figure 3-3

#### Indirect Indexed Addressing

This type of addressing takes one of two forms: <u>indirect preindexed</u>, or indirect postindexed.

When calculating a preindexed indirect address, the processor adds the value of the index register to the contents of the base register and displacement and uses the sum as an indirect address. It resolves any indirection chain and uses the result of the chain (or the indirect address itself, if there was no chain to follow) as the effective address.

When calculating a postindexed indirect address, the processor adds the contents of the base register and displacement and uses the result as an indirect address. It resolves any indirection chain, then adds the result of the chain (or the indirect address itself, if there was no chain to follow) to the contents of the specified index register to form the effective address.

# General Register Relative Addressing

General register relative (GRR) is an addressing capability added to 32I mode that speeds up big array accesses and often gives the effect of using general registers as base registers. The segment number is formed from bits 5 to 16 of the specified source register. The offset is formed in GRR by adding the displacement to bits 17 to 32 of the specified source register. GRR is used by the I mode instructions AIP and LIP. (GRR is not available for the earlier processors listed on page 1-1.)

#### ADDRESSING MODES

The first part of this chapter describes several ways to specify an address with information contained within an instruction. Once the processor calculates the effective address, it can reference whatever information is contained in the location specified by the effective address. This section describes the ways to specify an address in an instruction and how the processor forms the effective address.

The 50 Series processors support four modes of addressing, each of which forms addresses differently. Depending on the program and personal preference, one or two of these modes may be more useful than another. The three most important modes are:

- V, or virtual

- I, or general register

- R, or relative

The fourth mode -- S, or sectored, mode -- is supported for historical reasons.

#### V Mode

V mode performs short and long operations and has a wide variety of registers to use. A short (16-bit) instruction in this mode can reference the first 256 locations of both the stack and link, as well as the 224 locations on either side of the current location in the procedure segment. A long (32-bit) V mode instruction can directly reference all locations in four segments. Indirect addressing can reference all locations in up to 4096 128-Kbyte segments.

# I Mode

When referencing memory, I mode is similar to 32-bit V mode. The difference is that I mode short operations reference 8 32-bit general purpose registers for use as index registers, accumulators, counters, or the like. I mode long operations have the same referencing power as V mode long operations. They can also use immediate forms and five additional index registers. (This makes a total of 7 index registers that I mode long operations can use.) The index registers are specified by the source register field. General register 0, however, cannot be used for indexing.

General register relative (GRR) addressing is available only in I mode, and is used by the I mode instructions AIP and LIP. This form of addressing speeds up big array accesses and often gives the effect of using general registers as base registers. (GRR is not available for the earlier processors listed on page 1-1.)

The C language pointer is used by the I mode instructions ACP, OCP, DCP, ICP, LOC, SOC, and TCNP. The format of this pointer is the same as the indirect pointer, except that bit 4 is redefined as the B (byte) bit. When this bit contains 0, it indicates that bits 1 to 8 (the left byte) of an address contain the character to be used; when this bit contains 1, bits 9 to 16 (the right byte) of an address contain the character. A null pointer is represented by zeroes in bits 4 to 32. (The C language pointer and its instructions are not available for the earlier processors listed on page 1-1.)

Normal effective address formation uses either a base register, indirect pointer (IP) or a general register (for GRR addressing) as the source of the ring field, B bit, and segment number. The C language pointer is well defined for the IP and GRR form. When the base register is the source of the B bit, software depends on finding it reset to zero, pointing to the leftmost byte. While it is possible to set the E bit in a base register using 48-bit IPs to specify 32-bit addresses, this practice is not now done. Future implementations of V and I modes will force bit 4 to zero during effective address formation when the source of the segment is a base register; otherwise it will copy bit 4.

#### R Mode

A sector is a block of 512 (1000 octal) contiguous memory locations. Sector 0 starts on location 0 and ends on location '777; Sector 1 begins on location '1000 and ends on location '1777; and so on.

An R mode instruction can reference any location in Sector O, as well as a group of locations relative to the current value of the program counter. When the sector bit (S) in an R mode instruction is O, the instruction can only reference locations in Sector O. When S is 1, the instruction references locations relative to the current value of the program counter. The range of these relative locations is PC - '360 to PC + '377, inclusive.

An R mode instruction that specifies a location in the range PC - '361 to PC - '400, inclusive, selects a special addressing code, such as stack register. These special codes are explained in more detail in Tables 3-7 and 3-8.

#### S Mode

Like R mode instructions, S mode instructions contain a sector bit. When S is O, references are to Sector O. When S is 1, however, references are <u>only</u> to those locations within the sector containing the instruction.

Note that S mode is a holdover from early Prime machines that were based on the Honeywell 316 and 516 minicomputers. When operating in S mode, the 50 Series processors act exactly as these early machines do.

#### SUMMARY OF ADDRESSING MODES

The figures and tables in the rest of this chapter present summaries of each addressing mode. Table 3-1 is a list of the mnemonics used in these addressing mode summaries. Table 3-2 summarizes useful information about all the modes.

| Mnem | Explanation               |    | Mnem             | Explanation                          |

|------|---------------------------|----|------------------|--------------------------------------|

| BR I | Base register             | 11 | REG              | A location in the                    |

| СВ   | Class bit                 |    |                  | register file. See<br>Address Traps. |

| D    | Displacement              |    | S I              | Sector bit                           |

| DR   | Destination register      |    | SB               | Stack base register                  |

| F I  | Fault bit                 |    | SP               | Stack pointer                        |

| I I  | Indirect bit              |    | SR I             | Source register                      |

| LBI  | Link base register        |    | TM               | Tag modifier                         |

| OP   | Opcode                    |    | t<br>X I         | X index register                     |

| P I  | PC + 1                    |    | XB I             | Auxiliary base register              |

| PB I | Procedure base register** |    | ן<br><b>XX</b> ו | Opcode extension                     |

| PC I | Program counter**         |    | <br>Y            | Y index register                     |

Table 3-1 Mnemonics Used in Summaries of Addressing Modes\*

- \* An <u>H</u> appended to a register mnemonic refers to bits 1 to 16 of that register; an <u>L</u> so appended refers to bits 17 to 32.

- \*\* The PB segment number equals the PC segment number. The PB offset number is 0, but the PC offset number is the next instruction.

| Mode  <br>                 | Address  <br>Length | Addressing Range                                                                                 |                     | Indirection      |

|----------------------------|---------------------|--------------------------------------------------------------------------------------------------|---------------------|------------------|

| 16S direct                 | 14 bits             | 1024 halfwords                                                                                   | One I               | l                |

| 16S indirect               | 14 bits             | 16K halfwords                                                                                    | One I               | Multiple         |

| 32S direct                 | 15 bits             | 1024 halfwords                                                                                   | iOne I              | 1                |

| 32S indirect               | 15 bits             | 32K halfwords                                                                                    | One                 | Multiple         |

| 32R direct                 | 15 bits             | 1008 halfwords                                                                                   | One                 |                  |

| 32R indirect               | 15 bits             | 32K halfwords                                                                                    | iOne i              | Multiple         |

| 64R direct                 | 16 bits             | 1008 halfwords                                                                                   | One I               | 1                |

| 64R indirect               | 16 bits             | 64K halfwords                                                                                    | One I               | One              |

| 64V 16-bit<br>instructions | 16 bits             | 64K halfwords:<br>+256 SB relative<br>+256 LB relative<br>+/-256 PC relative<br>+512 PB absolute | One  <br> <br> <br> |                  |

| 64V 32-bit<br>instructions | 28 bits             | 4 segments*<br>                                                                                  | I Two               | One              |

| 64V indirect               | 28 bits             | 4096 segments*                                                                                   | I Two               | One I            |

| <br>  321 all<br>          | 28 bits             | 12 segments*<br>  with GRR**                                                                     | Seven               | i Ome i<br>i I I |

| 321 indirect               | 28 bits             | <br>  4096 segments*                                                                             | Seven               | One              |

Table 3-2 Summary of Addressing Modes

- \* All segments contain 128 Kbytes.

- \*\* Four segments for the earlier processors listed on page 1-1 because they have no GRR capability.

# 64V Mode Short Form

\_\_\_\_\_

Figure 3-4 and Table 3-3 display and explain 64V mode short form instructions.

64V Mode Formats, Short Form Figure 3-4

Table 3-3 64V Mode Short Form Summary

\_\_\_\_\_

| IIXIS         | Disp 1                               | Inst Type I        | Example i    | Form of EA                     |

|---------------|--------------------------------------|--------------------|--------------|--------------------------------|

|               |                                      | Direct  <br>Direct | LDA ADR      | REG  <br>SB+D                  |

|               |                                      | Direct@@           | I            | LB+D I                         |

| 101110        | 0-17@1]                              | Indexed            | LDA ADR,X    | REG, if D+X<'7;@               |

|               | 10-1377   ]                          | Indexed            |              | SB+D+X, if D+X>'7@  <br>SB+D+X |

|               |                                      | Indexed@@          | 1            | LB+D+X                         |

| 11010         |                                      |                    |              | I(REG)                         |

|               | ו 10-1 <b>777</b> ו                  |                    |              | I(PB+D)                        |

| 1   1   0     |                                      |                    |              | I(REG), if D+X<'7;@            |

|               | l lpi                                | reindexed          | 1            | I(PB+D+X),                     |

|               |                                      |                    | 1            | if D+X>'7@                     |

|               |                                      |                    | LDA ADR,X* I | I(PB+D+X)                      |

|               | ÷                                    | reindexed          | l.           |                                |

|               |                                      |                    | LDA ADR, *1  | I(PB+D)+X                      |

|               | l ipo                                | stindexed          | L            | 1                              |

| 0   0   1     | '- <b>34</b> 0-'+377  <sup>-</sup> I | Direct             | LDA ADR      | P+D I                          |

| 0   1   1     | '- <b>34</b> 0-'+ <b>377</b>   ]     | Indexed            | LDA ADR.1    | P+D+X                          |

| 1   0   1     | -340-+377 1                          |                    | LDA ADR, *   |                                |

| 1   1   1   1 | '-340-'+377 I                        |                    |              | •                              |

|               |                                      | eindexed           | <b></b> _    |                                |

|               |                                      |                    |              |                                |

# Notes to Table 3-3

- @ This table assumes segmented mode (modals bit 14 = 1). For nonsegmented mode, the displacement range is 0 to '37, rather than 0 to '7. This means that the range '10 to '377 changes to '40 to '377 in nonsegmented mode. The range '400 to '777 remains unchanged.

- @@ In these address forms, the displacement offsets the contents of LB by '400 (bit 8=1). To compensate for this, set the contents of LB to the current value of the link frame minus '400. For example, if the segment number in LB is '4002 and the offset number in the displacement is '177400, the offset of '400 gives the location of the link frame as segment number '4002, offset number 0.

This mode allows one level of indexing, and one of indirection.

REG refers to a location in the register file. See <u>Address</u> Traps at the end of this chapter.

The instructions DFLX, FLX, JSX, LDX, LDY, QFLX, STX, and STY do not do indexing. The effective address is formed as if bit 2 = 0.

# 64V Mode, Long Form and Indirect Form

| <br> | I | X       |       | OP         | 11     | 000      | I Y   | XX   | <u> </u> | BR           | I D  | ISP  | -<br> <br>- |

|------|---|---------|-------|------------|--------|----------|-------|------|----------|--------------|------|------|-------------|

|      |   |         |       | 33         |        |          |       |      | 48       |              |      |      |             |

|      |   |         |       |            | AU     | GMEN     | r co  | DE*  |          | -            |      |      |             |

|      |   |         |       | Ir         | nstr   | ucti     | on F  | orma | ıt       |              |      |      |             |

|      |   |         |       |            |        |          |       |      |          |              |      |      |             |

|      | 1 | 2       |       | 3          | 4 !    | 5        |       | 16   | 17       |              |      | 32   | ;           |

|      | F | ł I     | RIN   | <b>G</b> I | 0 1    | SEC      | GMEN  | r I  |          | OFF          | SET  |      | 1           |

|      |   | 3       | 32-]  | oit        | Ind    | irec     | t Poi | inte | r F      | orma         | t    |      |             |

|      |   |         |       |            |        |          |       |      |          |              |      |      |             |

| 12   |   | 3       | 4     | 5          |        | 16       | 17    | 3    | 2        | 33 3         | 3 37 | ,    | 48          |

|      |   | <br>! I | <br>ר |            | TRC MT | <br>7NTT |       |      |          | ————<br>ртти |      | ESER |             |

Figure 3-5 and Table 3-4 display and explain 64V mode long and indirect form instructions.

\* For quad operations only.

\*\* This indirect format is used only by a few instructions; most use the 32-bit form.

> 64V Mode Formats, Long Form and Indirect Form Figure 3-5

| ΙI  | X I      | ΥI | BR   | Instruction Type | Example       | Form of EA  |  |

|-----|----------|----|------|------------------|---------------|-------------|--|

| 0   | 0 1      | 0  | 00   | Direct           | LDA ADR       | PB/D        |  |

|     |          | ١  | 01   | 1                |               | SB+D        |  |

| 1   |          | I  | 10   | 1                |               | I LB+D      |  |

|     |          |    | 11   |                  | 1             | XB+D        |  |

| 0   | 0        | 1  | 00   | Indexed by Y     | IDA ADR,Y     | PB/D+Y      |  |

| 1   |          |    | 01 1 |                  | 1             | I SB+D+Y    |  |

|     |          |    | 10   | !                |               | ∣ LB+D+Y    |  |

| - 1 |          |    | 11   |                  | 1             | I XB+D+Y    |  |

| 0 1 | 11       | 0  | 00   | Indexed by X     | I LDA ADR,X   | PB/D+X      |  |

| I   |          |    | 01   | _                |               | I SB+D+X    |  |

| I   |          |    | 10 1 |                  | 1             | I LB+D+X    |  |

| I   |          |    | 11   | l                | 1             | I XB+D+X    |  |

| 0   | 1        | 1  | 00   | Indirect         | LDA ADR,*     | I(PB/D)     |  |

| _   | I        | 1  | 01   | 1                | 1             | I(SB+D)     |  |

|     | I        | I  | 10   | l                | I             | I(LB+D)     |  |

|     | l        | 1  | 11   | l                | I             | I(XB+D)     |  |

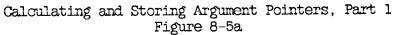

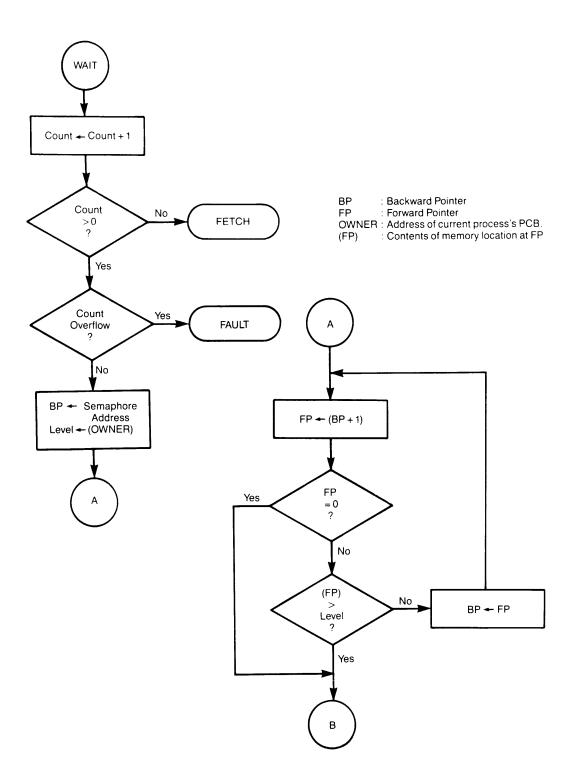

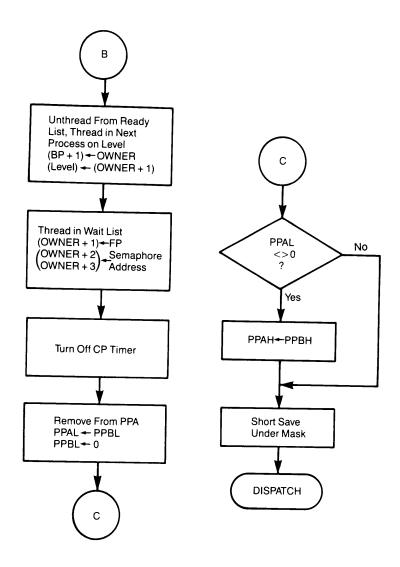

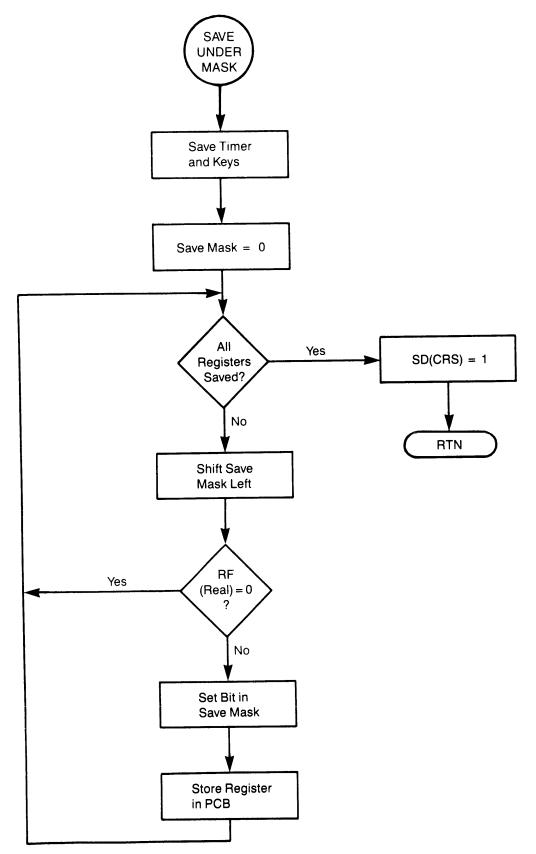

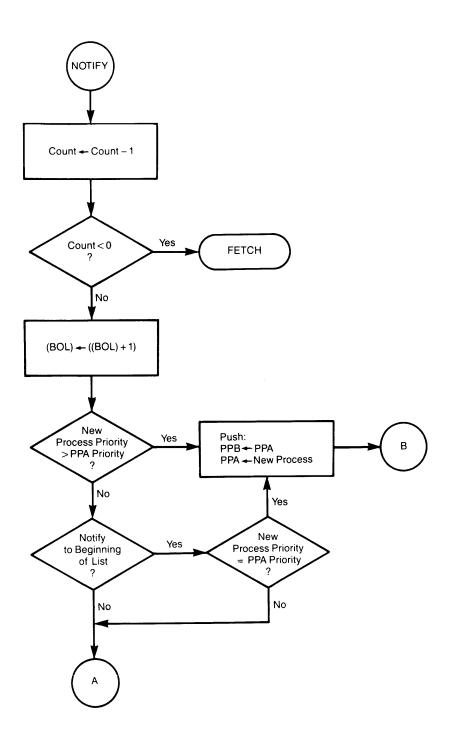

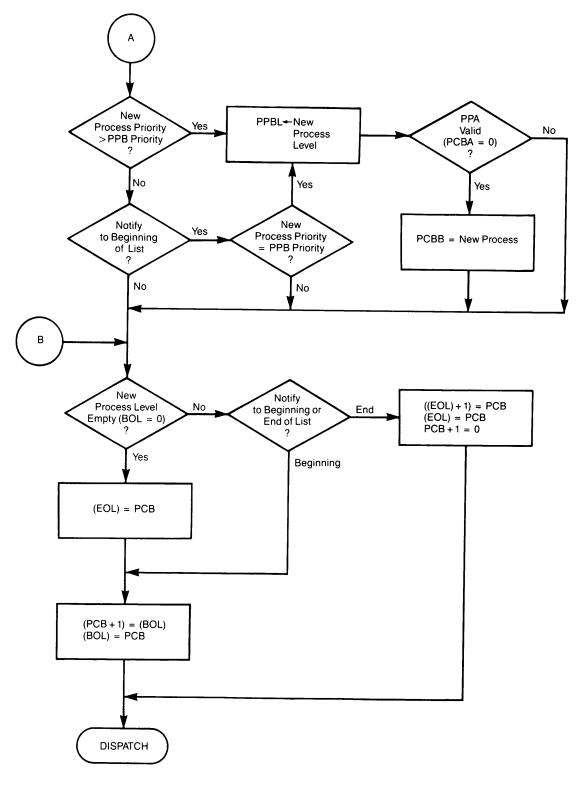

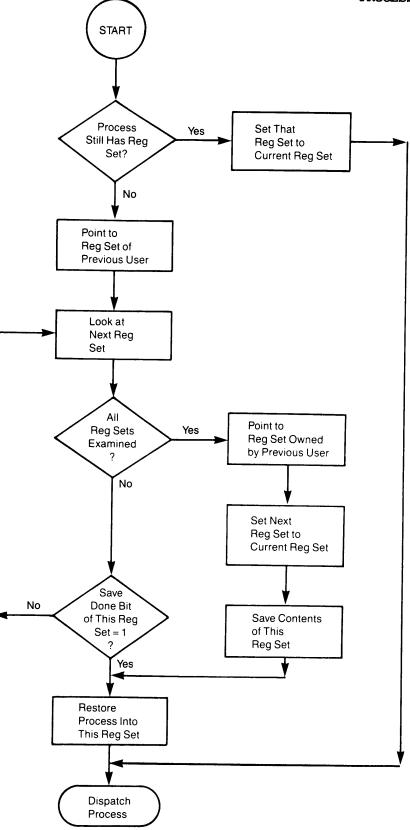

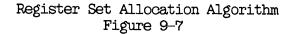

| 1   | 0        | 0  | 00   | Preindexed by Y  | I LDA ADR,Y*  | + I(PB/D+Y) |  |