# PRIME CUSTOMER SERVICE

# 50 SERIES COMPUTER SYSTEMS SERVICE MANUAL 070

MARCH

1985

#### NOTICE: THIS DOCUMENT CONTAINS PROPRIETARY INFORMATION

This document contains proprietary and confidential information of PRIME COMPUTER, INC. ("PRIME"). In consideration of the receipt of this document, the recipient agrees not to copy any of its contents, nor to disclose them to or allow them to be used by any person not currently a PRIME employee or an employee of the recipient having a need to know, without the express written consent of PRIME, and further agrees to surrender this document to PRIME when the reason for its receipt has terminated.

# COPYRIGHT INFORMATION

The information in this document is subject to change without notice and should not be construed as a commitment by Prime Computer Corporation. Prime Computer Corporation assumes no responsibility for any errors that may appear in this document.

The software described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license.

# Copyright © 1985 by Prime Computer, Incorporated Prime Park Way Natick, Massachusetts 01760

### Prime Computer, Incorporated Trademarks

The following are trademarks of Prime Computer, Incorporated:

| PRIME  | PRIMOS | PRIMENET | 50 S | SERIES |

|--------|--------|----------|------|--------|

| 150-11 | 250-11 | 550-11   | 750  | 850 🧳  |

#### CREDITS

| Technical Writer      | Dick McCretton |

|-----------------------|----------------|

| Editor                | Lisa Craycraft |

| Technical Illustrator | Lisa Kirouac   |

| Technical Typist      | Robin Flood    |

#### FOREWORD

Prime Computer Corporation is committed to a policy of providing the best possible service for our products and our customers. This manual has been prepared for use by Customer Service Representatives. It is intended to be used as a training aid and as a guide for installation, preventive and corrective maintenance.

The manual is organized into chapters based on tasks the Customer Service Representative performs at the customer's site. Tasks that are too difficult and time consuming to be performed on the customer's site are beyond the scope of the handbook.

Through experience and necessity Customer Service Representatives continually find methods to simplify Installation and Maintenance procedures. With the understanding that the best manuals are an organized collection of these field proven shortcuts, you are encouraged to forward all such procedures to Customer Service, Documentation.

Use of WARNING, CAUTION and NOTE is as follows:

- WARNING To warn the operator of a potentially hazardous condition that may cause physical injury.

- CAUTION To caution the operator of a condition that could cause damage to the equipment.

NOTE - To provide additional information.

MANUAL DEVICE(S) COVERED

٠,

۰.-۲.

-

2

PART NUMBER

| MAN010  | GE TERMINET 30                                                                                            | TEAMAN010    |

|---------|-----------------------------------------------------------------------------------------------------------|--------------|

| MAN020  | KENNEDY MAGNETIC TAPE                                                                                     | TEAMAN020    |

| MAN030  | P.E. FOX AND OWL                                                                                          | TEAMAN030    |

| MAN040  | CDC 40 & 80 MBYTE SMD                                                                                     | TEAMAN040    |

| MAN050  | DIABLO 44B MHD                                                                                            | TEAMAN050    |

| MAN060  | DATA PRINTER 300/600 LPM                                                                                  | TEAMAN060    |

| MAN070  | 50 SERIES COMPUTER SYSTEMS                                                                                | TEAMAN070-C  |

| MAN080  | SYSTEMS SOFTWARE                                                                                          | TEAMAN080    |

| MAN090  | CDC 32, 64 & 96 MBYTE CMD                                                                                 | TEAMAN090    |

| MAN100  | INTRODUCTION TO COMPUTER MAINTENANCE                                                                      | TEAMAN100    |

| MAN110  | PRINTRONIX MODEL 300 PRINTER                                                                              | TEAMAN110    |

| MAN120  | 300 MEGABYTE STORAGE MODULE DRIVE                                                                         | TEAMAN120-A  |

| MAN130  | TELEX 6250 BPI TAPE                                                                                       | TEAMAN130    |

| MAN140  | NEC SPINWRITER                                                                                            | TEAMAN140    |

| MAN150  | PW90 SERIES WORKSTATIONS                                                                                  | TEAMAN150    |

| MAN160  | DATAPRODUCTS PRINTER 300/600 LPM                                                                          | TEAMAN160    |

| MAN170  |                                                                                                           | TEAMAN170    |

| MAN180  | GE TERMINET 2030                                                                                          | TEAMAN180    |

| MAN200  | 2250 COMPUTER SYSTEM                                                                                      | TEAMAN200    |

| MAN210  | CAD GRAPHICS WORKSTATION (PW200)                                                                          | TEAMAN210    |

| MAN220  | CDC 675 MBYTE FMD                                                                                         | TEAMAN220    |

| MAN230  | 9000-ECL-CPU SYSTEMS                                                                                      | TEAMAN230-A1 |

| MAN240  | PRIME SYSTEM TERMINAL (PST100)                                                                            | TEAMAN240    |

| MAN250  | INTELLIGENT COMMUNICATIONS SUBSYSTEM                                                                      |              |

|         | MODEL II (ICS2)                                                                                           | TEAMAN250    |

| MAN270  | 2550 COMPUTER SYSTEM                                                                                      | TEAMAN270    |

| MAN280  | MAGNETIC STREAMING TAPE SUBSYSTEM<br>PRIME PRODUCER WORKSTATION (PW100)<br>300 MEGABYTE FIXED MODULE DISK | TEAMAN280    |

| MAN 290 | PRIME PRODUCER WORKSTATION (PW100)                                                                        | TEAMAN290    |

| MAN320  | 300 MEGABYTE FIXED MODULE DISK                                                                            | TEAMAN320    |

| MAN340  | LETTER QUALITY PRINTER (3185)                                                                             | TEAMAN340    |

| MAN350  | PT200 TERMINAL                                                                                            | TEAMAN350    |

| MAN360  | 9650 COMPUTER SYSTEM                                                                                      | TEAMAN360    |

| MAN900  | INTRODUCTION TO FIELD ENGINEERING                                                                         | TEAMAN900    |

iv

# RECORD OF CHANGES

| L<br>REV | EVEL:<br>UPDATE | ISSUE<br>DATE | NOTES/PAGES AFFECTED |

|----------|-----------------|---------------|----------------------|

| В        | 0               | 08/82         | Second Revision      |

| с        | 0               | 02/85         | Third Revision       |

|          |                 |               |                      |

|          |                 |               |                      |

|          |                 |               |                      |

|          |                 |               |                      |

|          |                 |               |                      |

|          |                 |               |                      |

|          |                 |               |                      |

|          |                 |               |                      |

|          |                 |               |                      |

|          |                 |               |                      |

|          |                 |               |                      |

|          |                 |               | 2                    |

|          |                 |               |                      |

|          |                 |               |                      |

|          |                 |               |                      |

|          |                 |               |                      |

|          |                 |               |                      |

|          |                 |               |                      |

|          |                 |               |                      |

|          |                 |               |                      |

|          |                 |               |                      |

|          |                 |               |                      |

|          |                 |               |                      |

:

v

. .

| CHAPTER 1. GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                   | 1- 1                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| <ul> <li>1.1 INTRODUCTION.</li> <li>1.2 SPECIFICATIONS.</li> <li>1.3 RELATED DOCUMENTATION.</li> <li>1.4 FCO LOG.</li> <li>1.5 EQUIPMENT IDENTIFICATION.</li> <li>1.6 PRIME MODEL NUMBERS.</li> <li>1.6.1 MARKETING SYSTEM NUMBERING SCHEME.</li> <li>1.6.2 INFORMATION SYSTEM NUMBERING SCHEME.</li> <li>1.6.3 PRIME TYPE NUMBERS.</li> </ul>   | $ \begin{array}{rrrrr} 1- & 4 \\ 1- & 7 \\ 1- & 7 \\ 1- & 7 \\ 1- & 8 \\ 1- & 8 \\ 1- & 9 \\ \end{array} $ |

| CHAPTER 2. INSTALLATION                                                                                                                                                                                                                                                                                                                          | 2 <del>-</del> 1                                                                                           |

| <ul> <li>2.1 INTRODUCTION.</li> <li>2.2 CHECKING FOR SHIPPING DAMAGE.</li> <li>2.3 UNPACKING INSTRUCTIONS.</li> <li>2.3.1 UNPACKING 50 SERIES CABINETS (NON-FCC).</li> <li>2.3.2 UNPACKING A 50 SERIES CABINET (FCC).</li> <li>2.3.3 PERIPHERALS.</li> </ul>                                                                                     | 2- 1<br>2- 1<br>2- 2<br>2- 5                                                                               |

| <ul> <li>2.3.4 MISCELLANEOUS ITEMS AND SOFTWARE BOXES.</li> <li>2.4 INVENTORY.</li> <li>2.5 SITE SURVEY.</li> <li>2.6 PRINTED CIRCUIT BOARD (PCB) CURRENT SPECIFICATIONS.</li> <li>2.7 VOLTAGE AND FREQUENCY CONVERSIONS.</li> <li>2.7.1 1045 POWER SUPPLY CONVERSION.</li> </ul>                                                                | 2- 7<br>2- 7<br>2- 8<br>2-10                                                                               |

| 2.7.2 1051 POWER SUPPLY CONVERSION<br>2.8 SYSTEM INSTALLATION<br>2.8.1 850 DUAL-CABINET (NON-FCC) INSTALLATION<br>2.8.1.1 Dual-Cabinet VCP Bezel Installation                                                                                                                                                                                    | 2-12<br>2-12<br>2-12                                                                                       |

| <ul> <li>2.8.1.2 Dual-Cabinet Interchassis I/O Cable<br/>Installation</li> <li>2.8.2 850 DUAL CABINET (FCC) INSTALLATION</li> <li>2.8.2.1 Joining The Cabinets</li> <li>2.8.2.2 Dual (FCC) Cabinet Inter-Cabinet Cabling</li> </ul>                                                                                                              | 2-16<br>2-16                                                                                               |

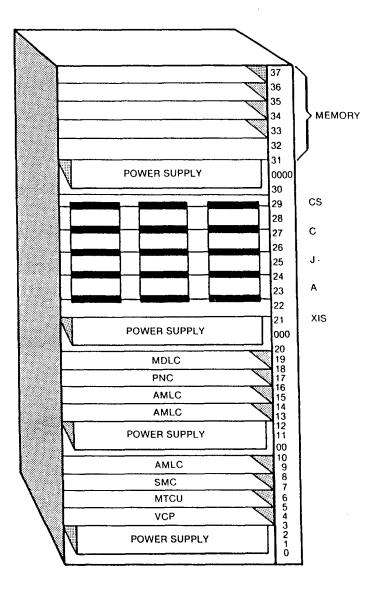

| 2.8.3 CPU VERIFICATION & TOP-HAT INSTALLATION<br>2.8.4 MEMORY BOARD INSTALLATION PROCEDURE<br>2.8.4.1 Handling E6, E7, E8 and E9 Memory Boards<br>2.8.4.2 Memory Configuration                                                                                                                                                                   | 2-20<br>2-20<br>2-23                                                                                       |

| 2.8.5 I/O CABLING GUIDELINES<br>2.8.5.1 I/O Cabling Guidelines For Non-FCC Cabinets<br>2.8.5.2 I/O Cabling For FCC Cabinets                                                                                                                                                                                                                      | 2-30<br>2-32                                                                                               |

| <pre>2.8.6 1045/1051 POWER SUPPLY INSTALLATION VERIFICATION<br/>2.8.7 UNINTERRUPTIBLE POWER SUPPLY INSTALLATION<br/>2.8.8 POWER DISTRIBUTION UNIT (PDU) CABLING<br/>2.8.8.1 Non-FCC Cabinet PDU Cabling<br/>2.8.8.1.1 Mainbay Cabinet (Domestic)<br/>2.8.8.1.2 Peripheral Cabinet (Domestic)<br/>2.8.8.1.3 Mainbay and Peripheral Cabinets</pre> | 2-39<br>2-39<br>2-40<br>2-40                                                                               |

| (International)<br>2.8.8.1.4 Free-Standing Peripherals<br>2.8.8.1.5 PDU Interconnections                                                                                                                                                                                                                                                         | 2-43                                                                                                       |

:

ł

| 2.8.8.2 FCC Cabinet PDU Cabling                                               |    |

|-------------------------------------------------------------------------------|----|

| 2.8.8.2.1 Power Supply Cables Installation 2-45                               |    |

| 2.8.8.3 Blower Power Cables Installation                                      | ,  |

| 2.8.9 SYSTEM CONSOLE INSTALLATION 2-47                                        | '  |

| 2.8.10 SYSTEM CONFIGURATION 2-48                                              | J  |

| 2.8.10.1 Disk Controller Configuration and Cabling 2-51                       | _  |

| 2.8.10.1.1 Model 4005 Disk Controller                                         |    |

| Configuration                                                                 | L  |

| 2.8.10.1.2 Model 4004 Disk Controller                                         |    |

| Configuration                                                                 |    |

| 2.8.10.1.3 Model 4004/4005 PROM Conversion 2-52                               |    |

| 2.8.10.1.4 Disk Controller Cabling 2-53                                       |    |

| 2.8.10.2 Tape Controller Device Address Conversion 2-54                       |    |

| 2.8.10.3 GCR Magnetic Tape Controller Configuration 2-55                      |    |

| 2.8.10.4 Kennedy Model Magnetic Tape Configuration 2-56                       | 5  |

| 2.8.10.5 Streaming Tape Subsystem (STS) Controller                            |    |

| Configuration 2-50                                                            | 6  |

| 2.8.10.6 Unit Record Controller (URC) Configuration 2-50                      |    |

| 2.8.10.6.1 URC Address Conversion 2-5                                         |    |

| 2.8.10.6.2 URC Cabling 2-5                                                    | 7  |

| 2.8.10.7 System Option Controller (SOC)                                       |    |

| Configuration and Address Conversion 2-5                                      |    |

| 2.8.10.7.1 SOC General Address Conversion 2-5                                 |    |

| 2.8.10.7.2 SOC Specific Address Conversion 2-6                                |    |

| 2.8.10.8 ICS1 Configuration                                                   |    |

| 2.8.10.8.1 ICS1 Address Conversion 2-6                                        |    |

| 2.8.10.8.2 ICS1 Cabling 2-6                                                   |    |

| 2.8.10.9 ICS2 Configuration 2-6<br>2.8.10.9.1 ICS2 Controller to Buffer Board | 4  |

| Cabling                                                                       | 5  |

| 2.8.10.9.2 ICS2 Buffer Board Configuration 2-6                                |    |

| 2.8.10.9.3 ICS2 LAC Bus Backplane Configuration 2-6                           |    |

| 2.8.10.9.4 ICS2 LAC Bus Power Supply                                          | U  |

| Configuration                                                                 | 6  |

| 2.8.10.9.5 ICS2 Asynchronous RS232 LAC                                        |    |

| Configuration                                                                 | 7  |

| 2.8.10.10 Asynchronous Multi-Line Controller (AMLC)                           | •• |

| Configuration                                                                 | 57 |

| 2.8.10.10.1 AMLC Address Conversion                                           |    |

| 2.8.10.10.2 AMLC Baud Rate Conversion 2-6                                     | 58 |

| 2.8.10.10.3 AMLC Cabling                                                      |    |

| 2.8.10.11 Synchronous Controller (MDLC)                                       |    |

| Configuration 2-7                                                             | 70 |

| 2.8.10.11.1 MDLC Address Conversion 2-7                                       | 71 |

| 2.8.10.11.2 MDLC Cabling 2-7                                                  |    |

| 2.8.10.12 PRIMENET Node Controller (PNC) System                               |    |

| Configuration 2-                                                              | 73 |

| 2.8.10.13 Main OR I/O Cabinet To Peripheral Cabinet                           |    |

| Cabling 2                                                                     |    |

| 2.8.10.14 Air Baffle Assembly Configuration 2-                                |    |

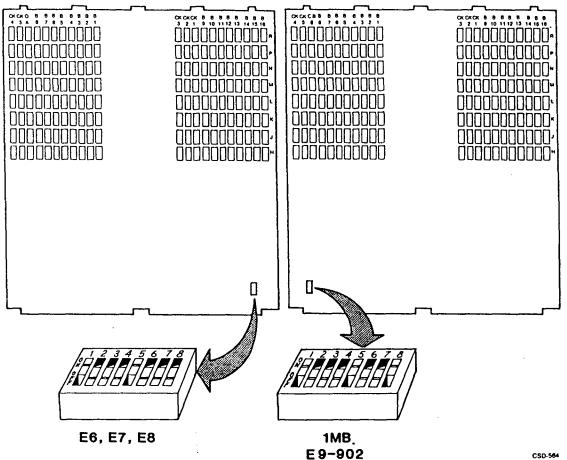

| 2.8.11 FREE-STANDING PERIPHERALS CABLING 2-                                   |    |

| 2.8.12 PERIPHERAL EQUIPMENT GROUNDING                                         |    |

| 2.9 INSTALLATION CHECKOUT 2-                                                  | 76 |

|               | 2.9.1 POWER-UP 2-76                                                             |

|---------------|---------------------------------------------------------------------------------|

|               | 2.9.2 LOADING OPERATING SYSTEM SOFTWARE                                         |

|               | 2.9.2.1 SMD Present: Loading OS From A Disk Pack 2-77                           |

|               | 2.9.2.2 No SMD: Loading OS From Tape 2-78                                       |

|               | 2.9.3 FINAL CHECKOUT                                                            |

| A Contraction |                                                                                 |

| СНАР          | TER 3. OPERATING INSTRUCTIONS                                                   |

| 3.1           | INTRODUCTION                                                                    |

| 3.2           | CONTROLS & INDICATORS                                                           |

|               | 3.2.1 SYSTEM STATUS PANEL CONTROLS AND INDICATORS 3-1                           |

|               | 3.2.1.1 Non-FCC Cabinet Status Panel                                            |

|               | 3.2.1.2 FCC Cabinet Status Panels 3- 3                                          |

|               | 3.2.2 POWER DISTRIBUTION UNIT CONTROLS AND INDICATORS 3-5                       |

| 3.3           | SYSTEM POWER-UP 3- 6                                                            |

| 3.4           | SYSTEM POWER-DOWN 3-8                                                           |

|               | 3.4.1 OPERATING SYSTEM SHUT-DOWN 3-8                                            |

|               | 3.4.1.1 PRIMOS Shut-down Procedure 3-8                                          |

|               | 3.4.1.2 PRIMOS II Shut-down Procedure                                           |

|               | 3.4.2 REMOVING SYSTEM POWER                                                     |

|               | 5 AUTOBOOT TO PRIMOS                                                            |

| 3.6           | 5 VIRTUAL CONTROL PANEL (VCP) OPERATION                                         |

|               | 3.6.1 CONTROL PANEL (CP) MODE                                                   |

|               | 3.6.1.1 Controlling Supervisor Terminal Output 3-12                             |

|               | 3.6.1.2 Halting the System 3-12                                                 |

|               | 3.6.1.3 Master Clearing the System 3-13                                         |

|               | 3.6.1.4 Booting the System 3-13                                                 |

|               | 3.6.1.5 Accessing Memory and Register Files 3-15                                |

|               | 3.6.1.5.1 Memory Addresses 3-15                                                 |

|               | 3.6.1.5.2 Data Representation                                                   |

|               | 3.6.1.5.3 Control Panel Commands                                                |

|               | 3.6.1.5.4 Memory Display Commands 3-17<br>3.6.1.5.5 Memory Access Commands 3-21 |

|               | 3.6.1.6 Accessing Physical (Unmapped) Memory 3-22                               |

|               | 3.6.1.7 Accessing Virtual (Mapped) Memory 3-22                                  |

|               | 3.6.1.8 Accessing Physical Register Files 3-22                                  |

|               | 3.6.1.9 Accessing CRS Register Files                                            |

|               | 3.6.1.10 Single-Stepping Instructions                                           |

|               | 3.6.1.11 Changing Processor Modes                                               |

|               | 3.6.1.12 Starting a Program (Placing it in "RUN") 3-24                          |

| •             | 3.6.1.13 Stopping Execution of a Program                                        |

|               | 3.6.1.14 Exiting Control Panel Mode 3-25                                        |

|               | 3.6.2 SYSTEM TERMINAL (ST) MODE                                                 |

|               | 3.6.3 ZCD MODE                                                                  |

| 3.            | 7 MULTI-STREAM PROCESSOR MULTI/UNI OPERATION                                    |

|               | 8 CHANGING I/O MASTERSHIP (MULTI-STREAM PROCESSOR)                              |

|               | 9 CHANGING SUPERVISOR TERMINAL BAUD RATE                                        |

| 3.            | 10 CHANGING BAUD RATE OF BOOT                                                   |

| 3.            | 11 T&MS                                                                         |

| × /           |                                                                                 |

| CHAPTER 4. PRINCIPLES OF OPERATION 4- 1                                |

|------------------------------------------------------------------------|

|                                                                        |

| 4.1 INTRODUCTION                                                       |

| 4.2 CENTRAL PROCESSOR UNIT (CPU)                                       |

| 4.2.1 CPU FUNCTIONAL DESCRIPTION                                       |

| 4.2.2 TIMING AND CONTROL UNIT                                          |

| 4.2.3 ARTHMETIC UNIT                                                   |

| 4.2.4 PIERIORI PENAGEMENT: $4-7$<br>4.2.5 OPERATING MODES. $4-7$       |

| 4.2.5 OFENALING HOLES $4^{-7}$<br>4.2.5.1 Absolute Addressing $4^{-8}$ |

| 4.2.5.2 Virtual (Segmented/Paging) Addressing 4-8                      |

| 4.2.6 SEGMENT TABLE LOOKASIDE BUFFER (STLB)                            |

| 4.2.7 CACHE MEMORY. $4-10$                                             |

| 4.2.7.1 CPU Cache Reads                                                |

| 4.2.7.2 CPU Cache Writes 4-11                                          |

| 4.2.7.3 DMX Cache Cycles 4-11                                          |

| 4.2.7.4 Cache/STLB Summary 4-11                                        |

| 4.2.8 REFRESH 4-11                                                     |

| 4.2.9 PROCESSOR MANAGEMENT 4-11                                        |

| 4.2.9.1 Process Exchange 4-12                                          |

| 4.2.9.2 Procedure Call 4-13                                            |

| 4.2.10 ERROR MANAGEMENT                                                |

| 4.2.10.1 Traps                                                         |

| 4.2.10.2 Faults                                                        |

| 4.2.10.2.1 Restricted Instruction                                      |

| 4.2.10.2.2 Unimplemented Instruction                                   |

| 4.2.10.2.3 Illegal Instruction 4-15                                    |

| 4.2.10.3 Checks 4-15<br>4.2.10.3.1 Machine Checks                      |

| 4.2.10.3.1 Machine Checks                                              |

| 4.2.10.3.3 Memory Parity                                               |

| 4.2.10.3.4 I/O Parity                                                  |

| 4.2.10.4 Interrupts                                                    |

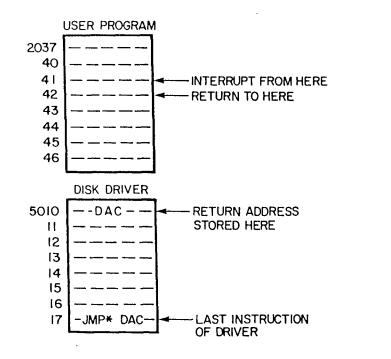

| 4.2.10.4.1 Device Driver Programs                                      |

| 4.2.10.4.2 Program Vectoring                                           |

| 4.2.10.4.3 Interrupt Modes 4-21                                        |

| 4.2.10.4.4 Interrupts in Process Exchange Mode 4-22                    |

| 4.2.10.4.5 Memory Increment Interrupts 4-22                            |

| 4.2.10.4.6 Interrupt Inhibits/Enables                                  |

| 4.2.10.4.7 Override Inhibits                                           |

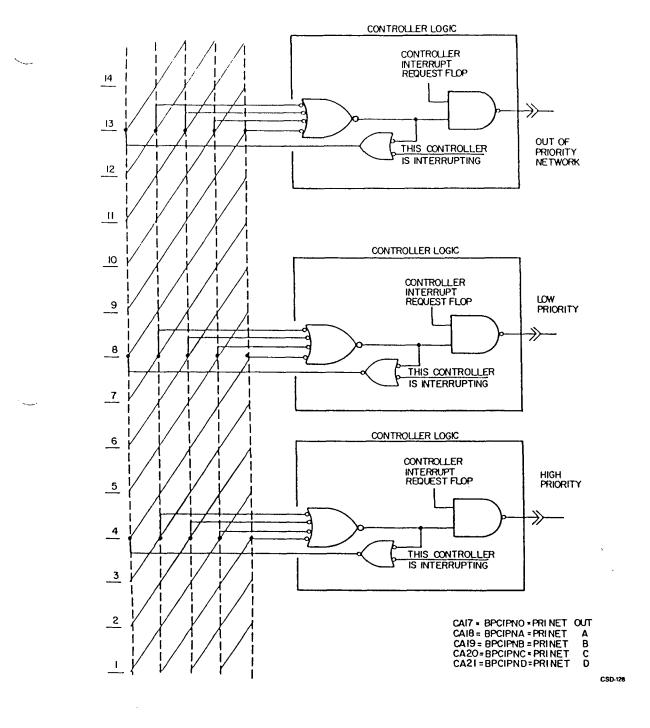

| 4.2.10.4.8 Interrupt Priority Network                                  |

| 4.2.10.4.9 Highest Priority Active Interrupt 4-24                      |

| 4.2.11 PERIPHERAL I/O MANAGEMENT                                       |

| 4.2.11.1 Programmed I/O (PIO)                                          |

| 4.2.11.1.1 Output/Input The A Register (OTA/INA) 4-27                  |

| 4.2.11.1.2 Skip On Condition Set (SKS) 4-27                            |

| 4.2.11.1.3 Output Control Pulse (OCP)                                  |

|                                                                        |

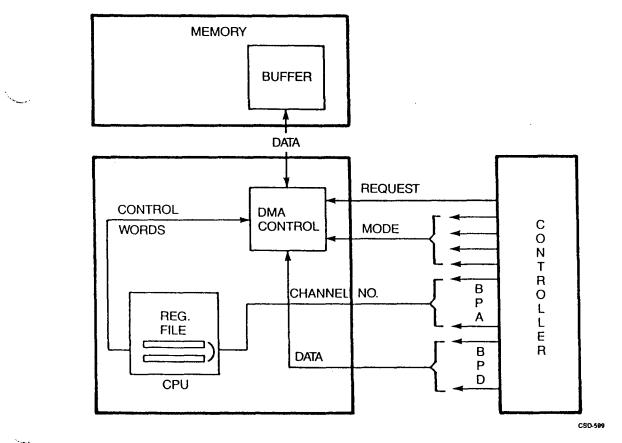

| 4.2.11.2.1 Direct Memory Access (DMA)                                  |

| 4.2.11.2.2 Direct Memory Channel (DMC)                                 |

| 4.2.11.2.4 Direct Memory Queue (DMQ)                                   |

| 4.2.11.2.5 Burst Mode DMA (BDMA)                                       |

|     | 4.2.11.2.6 DMX Priority Network                          | 1-39         |

|-----|----------------------------------------------------------|--------------|

|     | 4.2.12 ADDITIONAL PROCESSOR FEATURES                     | 1-10         |

|     | 4.2.12.1 Extended Instruction Set (P500)                 |              |

|     |                                                          | 4-42         |

|     |                                                          | 4-43         |

|     |                                                          | 4-43<br>4-44 |

|     | 4.2.12.4 Stream Synchronization Unit (SSU)               |              |

|     |                                                          | 4-45         |

|     |                                                          | 4-46         |

|     |                                                          | 4-49         |

| 1 2 |                                                          | 4-50         |

| 4.3 | MAIN MEMORY.                                             | 4-51         |

|     |                                                          | 4-51         |

|     |                                                          | 4-52         |

|     |                                                          | 4-54         |

|     |                                                          | 4-55         |

|     | 4.3.4.1 Wide-Word Interleaved Read                       | 4-55         |

|     | 4.3.4.2 Wide-Word Interleaved Write                      |              |

|     | 4.3.5 MEMORY ERROR CHECKING AND CORRECTING (ECCC)        | 4-56         |

|     | 4.3.5.1 ECCC Memory Write Operation                      | 4-57         |

|     | 4.3.5.2 ECCC Memory Read Operation                       | 4-57         |

|     | 4.3.6 MEMORY TYPE SELECTION.                             | 4-58         |

|     | 4.3.7 MEMORY SLOT SELECTION.                             | 4-58         |

| 4.4 | CHASSIS AND BACKPLANE                                    |              |

|     |                                                          | 4-59         |

|     | 4.4.2 BACKPLANE                                          |              |

|     | 4.4.2.1 Major Backplane Buses                            |              |

|     | -4.4.2.2 Backplane Bus Signals                           |              |

|     |                                                          | 4-70         |

| 4.5 |                                                          | 4-75         |

|     |                                                          | 4-76         |

|     |                                                          | 4-77         |

|     | 4.5.3 DISK CONTROLLER (SMC).                             | 4-77         |

|     |                                                          | 4-77         |

|     | 4.5.5 UNIT RECORD CONTROLLER (URC).                      | 4-77         |

|     | 4.5.6 SYSTEM OPTION CONTROLLER (SOC).                    |              |

| 16  | COMMUNICATIONS I/O CONTROLLERS.                          | 4-//         |

| 4.0 | 4.6.1 PRIMENET NODE CONTROLLER.                          | 4-77         |

|     | 4.6.1.1 PRIMENET Network Information                     |              |

|     |                                                          |              |

|     | 4.6.1.2 PRIMENET Network Operation.                      | 4-79         |

|     | 4.6.2 ASYNCHRONOUS MULTI-LINE CONTROLLER (AMLC)          |              |

|     | 4.6.2.1 AMLC & QAMLC Functional Operation                |              |

|     | 4.6.2.2 AMLC Initialization                              |              |

|     | 4.6.2.3 AMLC Transmit Operation                          |              |

|     | 4.6.2.4 AMLC Receive Operation                           |              |

|     | 4.6.2.5 AMLC Status Reporting                            |              |

|     | 4.6.2.6 AMLC Interrupts                                  |              |

|     | 4.6.2.7 UART Functional Operation                        |              |

|     | 4.6.3 MULTI-DATA LINK CONTROLLER (MDLC)                  |              |

| • - | 4.6.4 INTELLIGENT COMMUNICATIONS SUBSYSTEM (ICS1 & ICS2) |              |

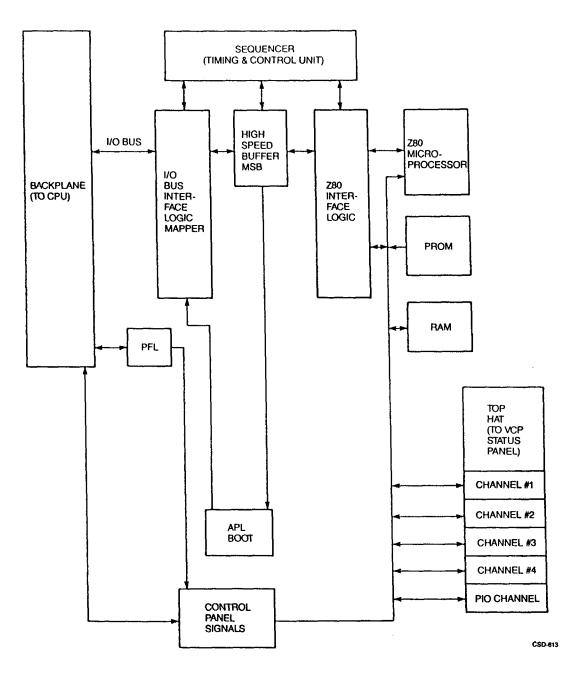

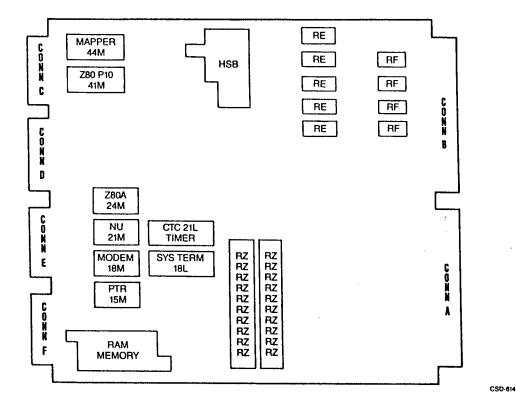

| 4.7 | 7 VIRTUAL CONTROL PANEL (VCP)                            | 4-87         |

|     | 4.7.1 VCP INTERFACE                                      | 4-89         |

|     | 4.7.2 VCP IMPLEMENTATION OF PIO COMMANDS                 |              |

|     | 4.7.3 Z80 CODE DEBUGGER                                  | 1-90         |

| 4.8 P<br>4<br>4<br>4<br>4<br>4<br>4.9 P | 7.4 VCP CONNECTOR SIGNALS.4-91OWER SUPPLIES.4-95.8.1 1045 AND 1051 POWER SUPPLIES.4-96.8.2 DC VOLTAGE BUSES.4-96.8.3 POWER SUPPLY PROTECTION.4-96.8.4 AC/DC POWER FAILURE SEQUENCE AND CONTROLS.4-98.8.5 UNINTERRUPTIBLE POWER SUPPLY (UPS).4-98OWER DISTRIBUTION UNIT (PDU) NON-FCC CABINET.4-99POWER DISTRIBUTION UNIT (PDU) FCC.4-102 |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHAPTE                                  | R 5. PREVENTIVE MAINTENANCE                                                                                                                                                                                                                                                                                                              |

| 5.1 T                                   | NTRODUCTION                                                                                                                                                                                                                                                                                                                              |

|                                         | AINTENANCE PHILOSOPHY                                                                                                                                                                                                                                                                                                                    |

|                                         | RODUCT HISTORY                                                                                                                                                                                                                                                                                                                           |

|                                         | 3.1 SYSTEM LOGBOOK                                                                                                                                                                                                                                                                                                                       |

|                                         | .3.2 EVENT LOGGERS                                                                                                                                                                                                                                                                                                                       |

| 5                                       | 5.3.2.1 System Event Logger                                                                                                                                                                                                                                                                                                              |

|                                         | 5.3.2.2 Network Event Logger                                                                                                                                                                                                                                                                                                             |

| 5.4 P                                   | M SCHEDULE. 5-7                                                                                                                                                                                                                                                                                                                          |

|                                         | AINTENANCE TOOLS. 5-9                                                                                                                                                                                                                                                                                                                    |

|                                         | M PROCEDURE. 5-9                                                                                                                                                                                                                                                                                                                         |

|                                         | 5-6.1 SYSTEM SHUTDOWN                                                                                                                                                                                                                                                                                                                    |

|                                         | 5.6.2 CLEANING AND INSPECTION                                                                                                                                                                                                                                                                                                            |

|                                         | 6.6.3 PERIPHERALS. 5-11                                                                                                                                                                                                                                                                                                                  |

|                                         | 5.6.3.1 Disk Drives (Removable)                                                                                                                                                                                                                                                                                                          |

|                                         | 5.6.3.2 Magnetic Tape Drives                                                                                                                                                                                                                                                                                                             |

|                                         | 5.6.3.3 System Console (TERMINET)                                                                                                                                                                                                                                                                                                        |

|                                         | 5.6.3.4 Printers                                                                                                                                                                                                                                                                                                                         |

|                                         | 5.6.3.5 Terminals (CRTS)                                                                                                                                                                                                                                                                                                                 |

| 5.7 F                                   | ENVIRONMENTAL CHECKOUT. 5-12                                                                                                                                                                                                                                                                                                             |

|                                         | SYSTEM STARIUP                                                                                                                                                                                                                                                                                                                           |

|                                         | 5 12                                                                                                                                                                                                                                                                                                                                     |

| CHAPTE                                  | R 6. CORRECTIVE MAINTENANCE                                                                                                                                                                                                                                                                                                              |

|                                         |                                                                                                                                                                                                                                                                                                                                          |

|                                         | CORRECTIVE MAINTENANCE OVERVIEW                                                                                                                                                                                                                                                                                                          |

|                                         | 5.1.1 MAINTENANCE TOOLS & MATERIALS                                                                                                                                                                                                                                                                                                      |

|                                         | 5.1.2 LOGIC LEVELS 6- 1                                                                                                                                                                                                                                                                                                                  |

|                                         | TROUBLESHOOTING GUIDE                                                                                                                                                                                                                                                                                                                    |

|                                         | 6.2.1 GENERAL TROUBLESHOOTING NOTES                                                                                                                                                                                                                                                                                                      |

| (                                       | 6-2                                                                                                                                                                                                                                                                                                                                      |

|                                         | 6.2.2.1 VCP Dynamic RAM Test 6- 2                                                                                                                                                                                                                                                                                                        |

|                                         | 6.2.2.2 VCP High Speed Buffer Test 6- 3                                                                                                                                                                                                                                                                                                  |

| (                                       | 6.2.3 MICRO-VERIFY ERROR HANDLING                                                                                                                                                                                                                                                                                                        |

|                                         | 6.2.3.1 Micro-Verify Initialization                                                                                                                                                                                                                                                                                                      |

|                                         | 6.2.3.2 P850/P750 Micro-Verify Differences 6- 4                                                                                                                                                                                                                                                                                          |

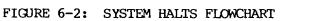

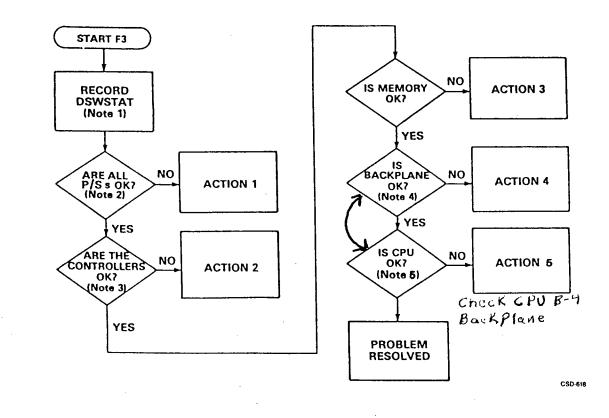

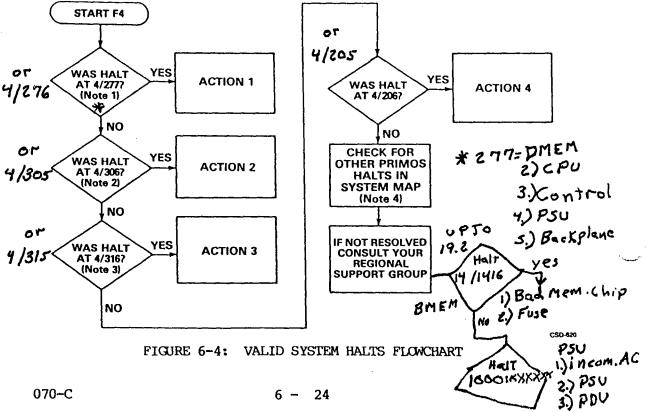

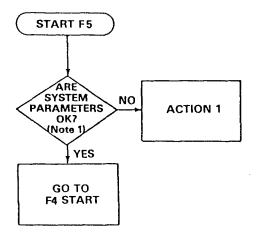

| l l                                     | 6.2.4 TROUBLESHOOTING SYSTEM (PRIMOS) HALTS                                                                                                                                                                                                                                                                                              |

|                                         | 6.2.4.1 Hardware Diagnostic Status Registers 6-10                                                                                                                                                                                                                                                                                        |

|                                         | 6.2.4.2 General System Halt Handling                                                                                                                                                                                                                                                                                                     |

|                                         | 6.2.4.2.1 850 Halts 6-13                                                                                                                                                                                                                                                                                                                 |

|                                         | 6.2.4.2.2 SSU Halts                                                                                                                                                                                                                                                                                                                      |

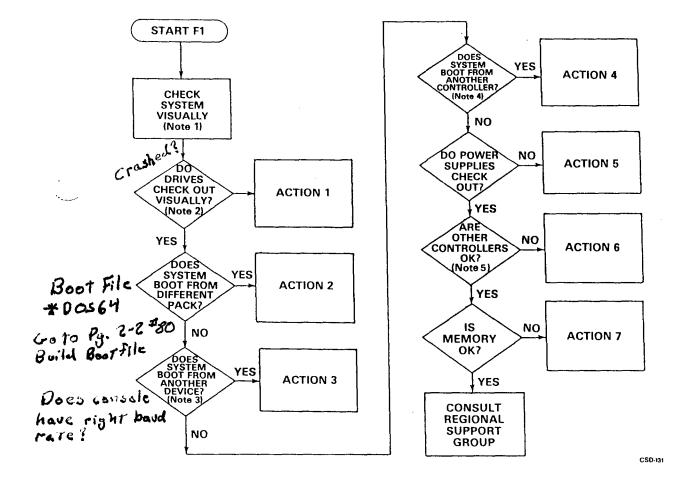

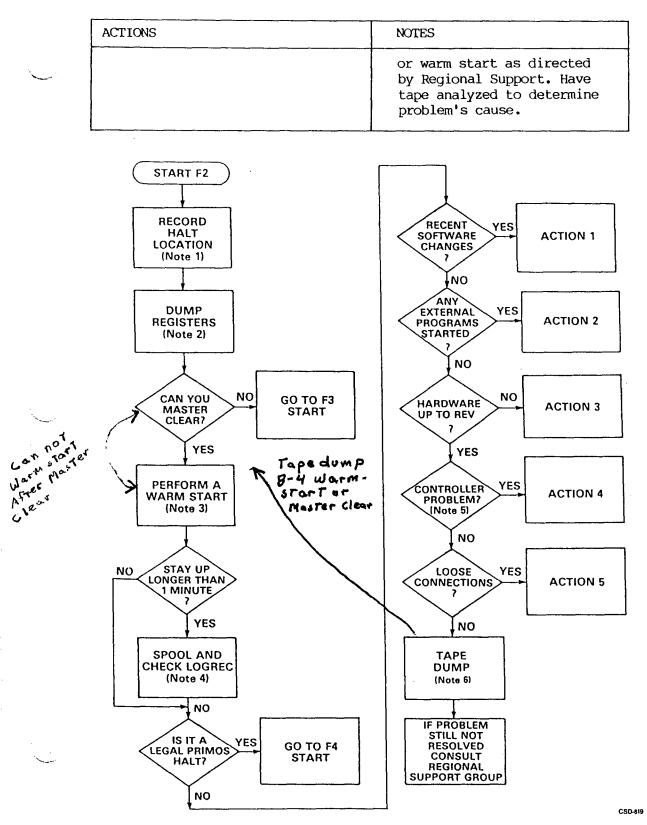

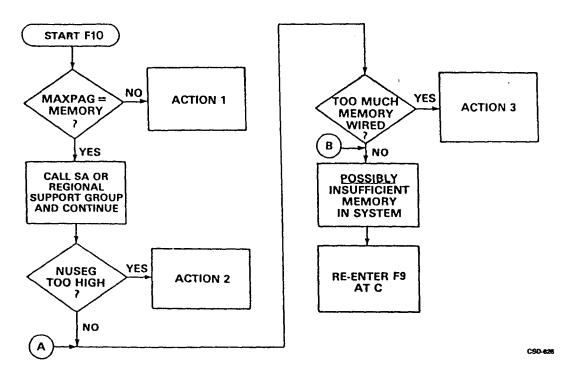

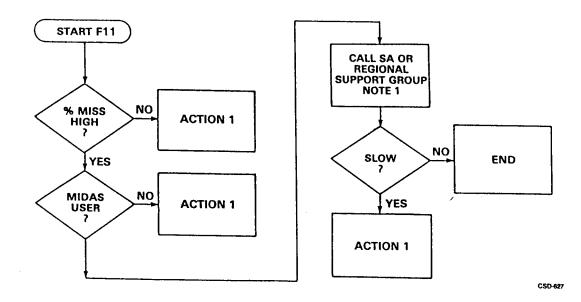

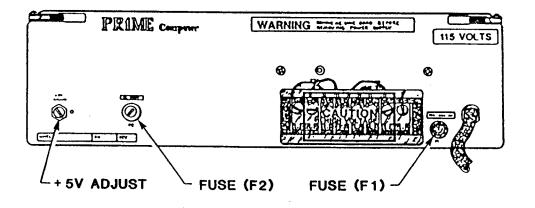

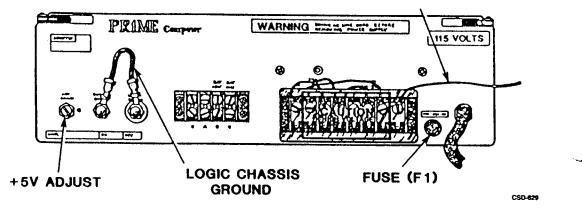

| 6.2.4.3 Memory ECCU Error (MEMPA) Handling.<br>6.2.4.4 Machine Check Handling.<br>6.2.4.5 Troubleshooting Flowcharts.<br>6.2.5 TROUBLESHOOTING COMMON SYSTEM PROBLEMS.<br>6.2.6 TROUBLESHOOTING WITH LOGREC.<br>6.2.6.1 LOGREC Disk Errors.<br>6.2.6.2 LOGREC Machine Checks.<br>6.2.6.3 LOGREC Memory Parity.<br>6.2.6.3.1 LOGREC Memory Parity Format.<br>6.2.6.3.2 Memory ECCC Error Handling.<br>6.2.6.4 LOGREC Missing Memory Errors.<br>6.3 1045/1051 POWER SUPPLY MEASUREMENTS AND ADJUSTMENTS. | 6-16<br>6-17<br>6-28<br>6-38<br>6-39<br>6-40<br>6-40<br>6-41<br>6-41<br>6-41 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| CHAPTER 7. PARTS REMOVAL AND REPLACEMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7- 1                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>-</b> 7 1                                                                 |

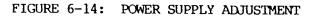

| 7.1 FRU REMOVAL/REPLACEMENT PROCEDURES<br>7.1.1 PRINTED CIRCUIT BOARD (PCB) REMOVAL/REPLACEMENT                                                                                                                                                                                                                                                                                                                                                                                                        | /- 1<br>7 1                                                                  |

| 7.1.1.1 PCB Removal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7-1                                                                          |

| 7.1.1.2 PCB Replacement.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                              |

| 7.1.2 MEMORY BOARD RAM REMOVAL/REPLACEMENT.                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7 1                                                                          |

| 7.1.3 NON-FCC CABINET FRU REMOVAL/REPLACEMENT PROCEDURES                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                              |

| 7.1.3.1 PDU Removal/Replacement                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7-4                                                                          |

| 7.1.3.2 Cabinet Blower Removal/Replacement                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                              |

| 7.1.3.3 Power Supply Removal/Replacement                                                                                                                                                                                                                                                                                                                                                                                                                                                               | /- 4                                                                         |

| 7.1.3.4 16-Slot and 19-Slot Backplane                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                              |

| Removal/Replacement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | /- 5                                                                         |

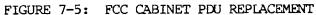

| 7.1.4 FCC CABINET FRU REMOVAL/REPLACEMENT PROCEDURE                                                                                                                                                                                                                                                                                                                                                                                                                                                    | /- 5                                                                         |

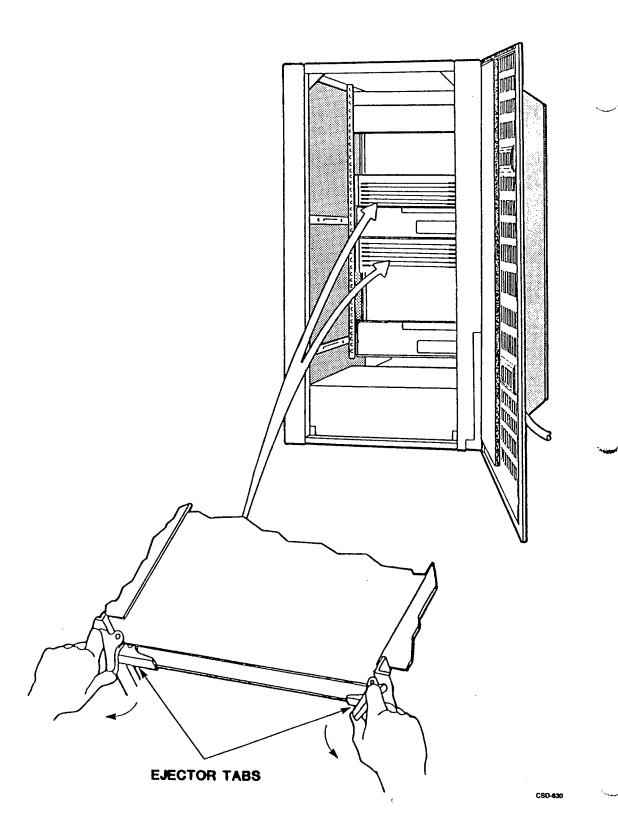

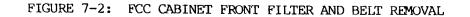

| 7.1.4.1 Blower Front Air Filter Removal/Replacement                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                              |

| 7.1.4.2 Blower Bottom Air Filter Replacement                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                              |

| 7.1.4.3 Cabinet Blower Assembly Removal/Replacement                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                              |

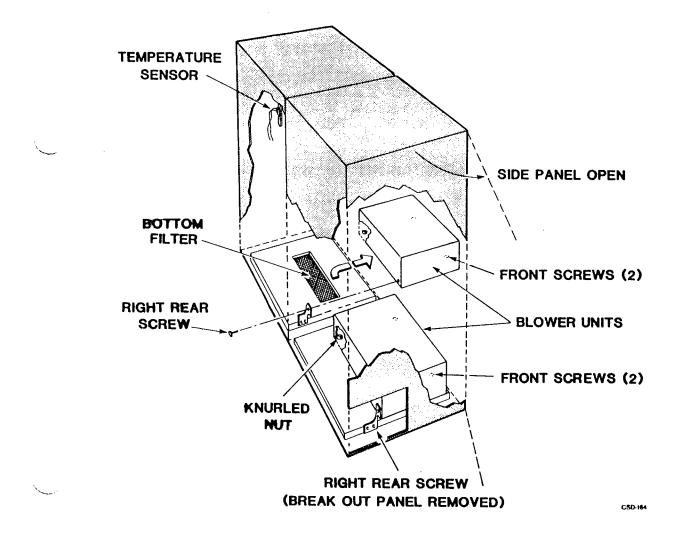

| 7.1.4.4 Blower Belt Removal/Replacement                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                              |

| 7.1.4.5 Blower Vane Switch Removal/Replacement                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                              |

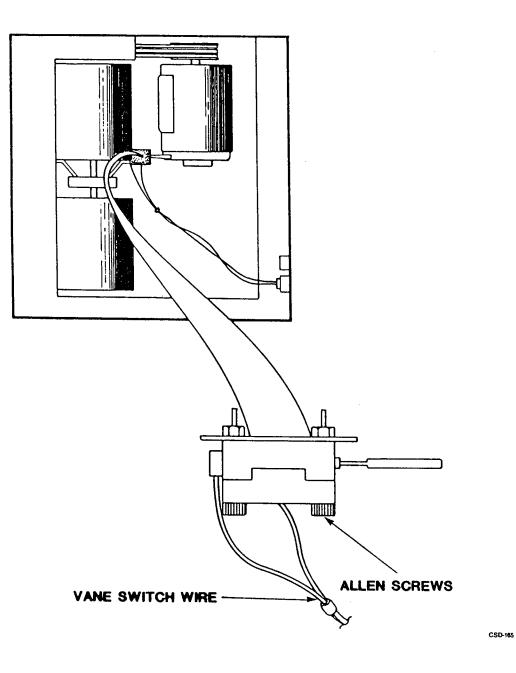

| 7.1.4.6 Power Supply Removal/Replacement                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7-8                                                                          |

| 7.1.4.7 Power Distribution Unit (PDU)                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                              |

| Removal/Replacement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7- 8                                                                         |

| 7.1.4.8 16-slot and 19-Slot Backplane                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                              |

| Removal/Replacement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7-11                                                                         |

| 7.2 50 SERIES FRUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7-12                                                                         |

.

. . •

.

.

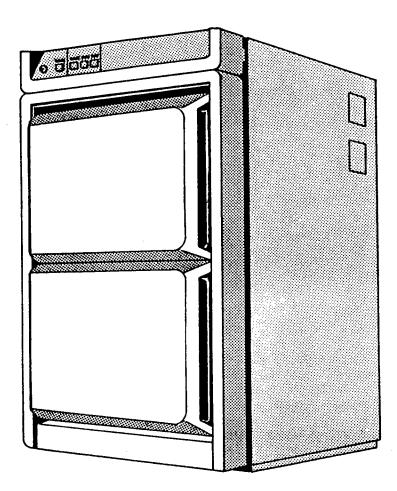

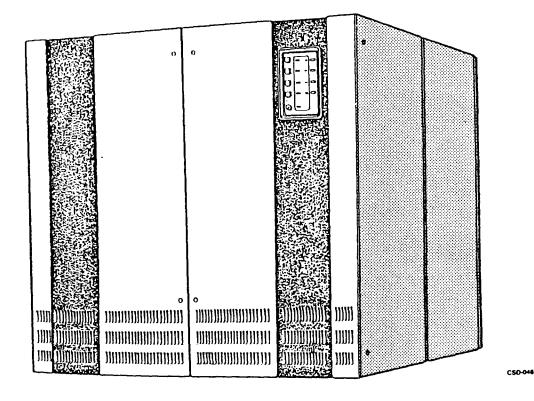

| FIGURE 1-1:                    | 150-II/250-II/550-II CPU SYSTEM (NON-FCC) 1- 1          |

|--------------------------------|---------------------------------------------------------|

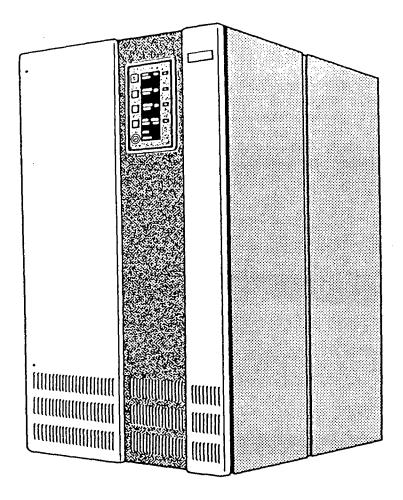

| FIGURE 1-2:                    | 150-II/250-II/550-II CPU SYSTEM (FCC) 1- 2              |

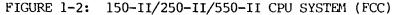

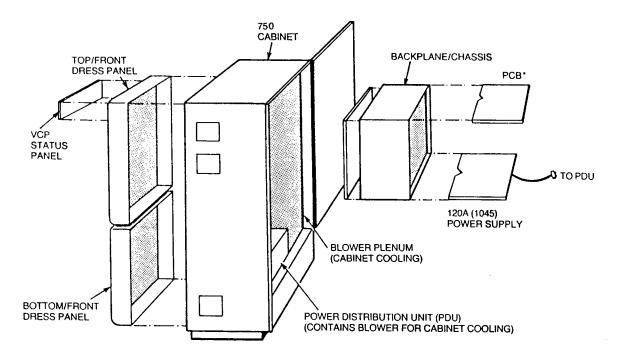

| FIGURE 1-3:                    | 750/850 CPU SYSTEM (NON-FCC) 1- 3                       |

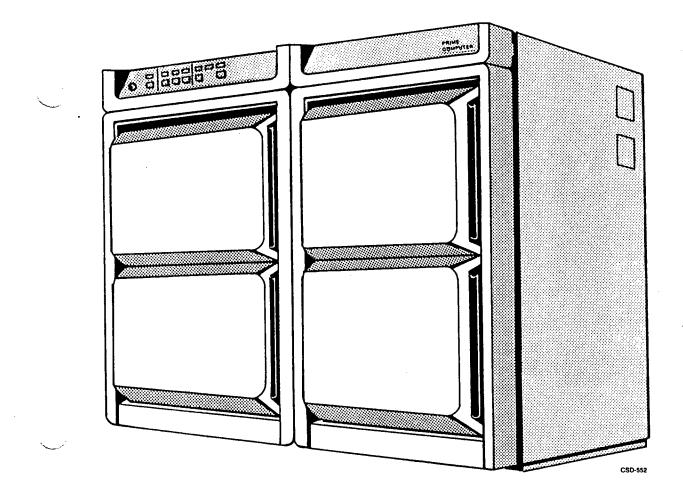

| FIGURE 1-4:                    | 750/850 CPU SYSTEM (FCC) 1- 4                           |

| TABLE 1-1:                     | GENERAL SPECIFICATIONS: 150, 250-II, 550-II SYSTEMS 1-4 |

| TABLE 1-2:                     | GENERAL SPECIFICATIONS: 750 & 850 SYSTEMS 1-5           |

| TABLE $1-3$ :                  | CABINET GENERAL DIMENSIONS                              |

| TABLE $1-3$ :                  |                                                         |

| TABLE $1-4$ :<br>TABLE $1-5$ : | 50 SERIES WEIGHT                                        |

| TABLE $1-5$ :<br>TABLE $1-6$ : |                                                         |

|                                | 50 SERIES CONFIGURATIONS 1-10                           |

| TABLE 1-7:                     | INFORMATION SYSTEM (DEALER) CONFIGURATIONS 1-12         |

| TABLE 1-8:                     | COMMON PRIME TYPE NUMBERS 1-13                          |

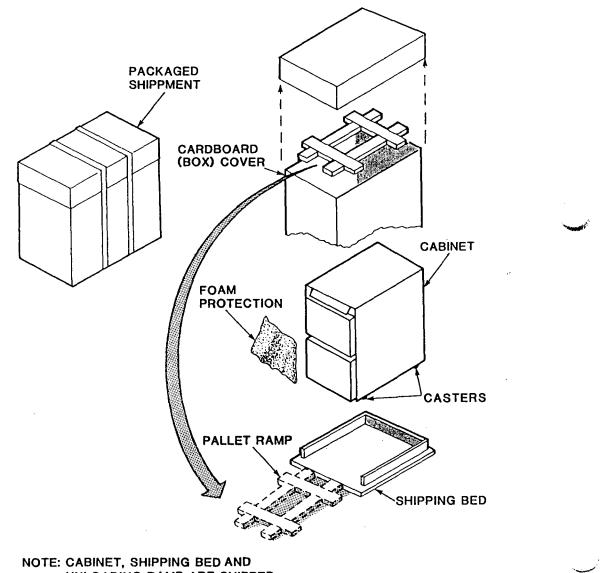

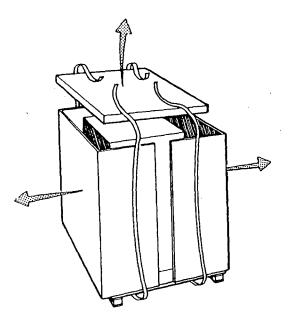

| FIGURE 2-1:                    | UNPACKING THE NON-FCC CABINET 2- 2                      |

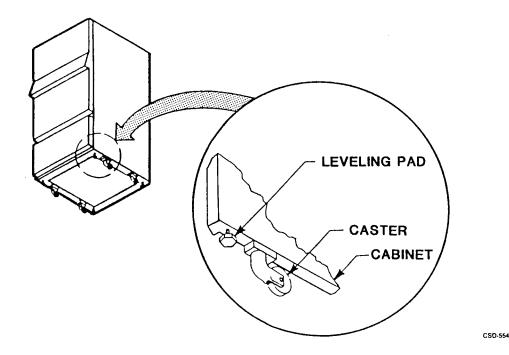

| FIGURE $2-2$ :                 | CABINET LEVELING PADS                                   |

| FIGURE 2-2:                    |                                                         |

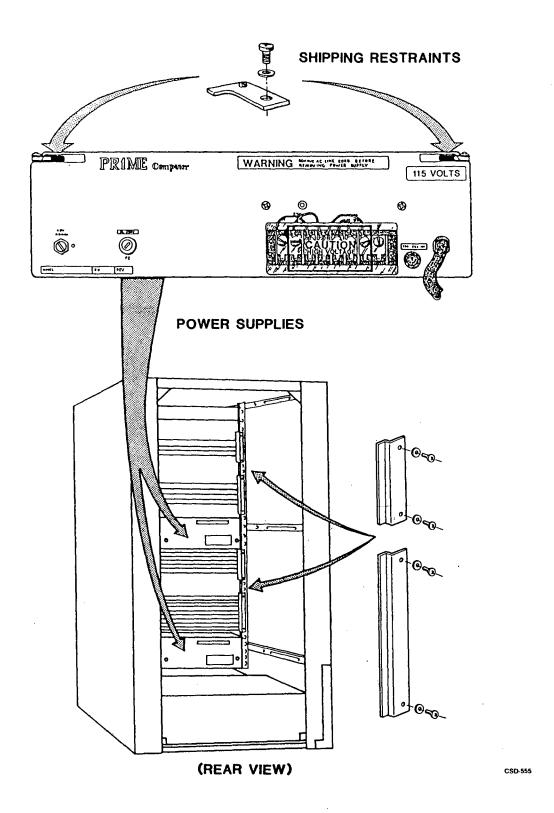

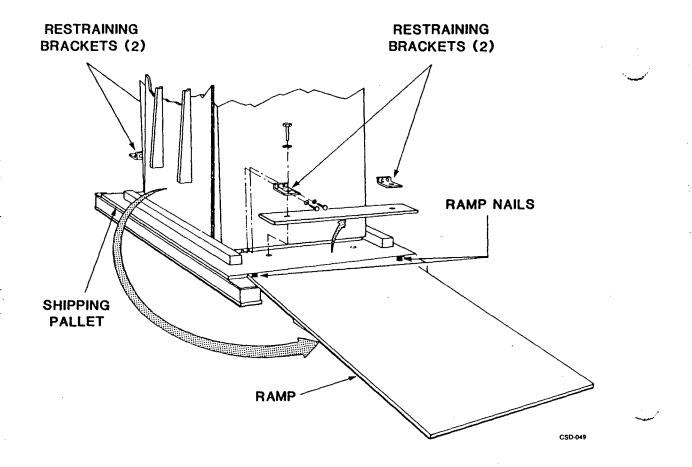

|                                | SHIPPING RESTRAINTS REMOVAL                             |

| FIGURE 2-4:                    | UNPACKING THE FCC CABINET 2- 6                          |

| TABLE 2-1:                     | ELECTRICAL SPECIFICATIONS 2-7                           |

| TABLE 2-2:                     | ENVIRONMENTAL SPECIFICATIONS: 2-7                       |

| TABLE 2-3:                     | POWER CORDS AND CONNECTORS 2-8                          |

| TABLE 2-4:                     | OPERATING SPECIFICATIONS: DC CURRENT DRAW PER BOARD 2-9 |

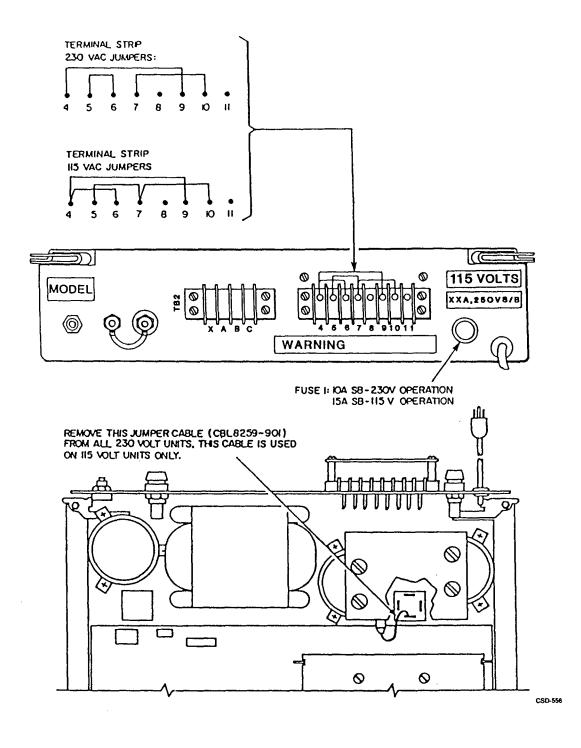

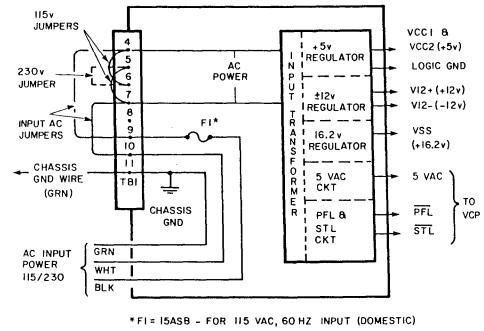

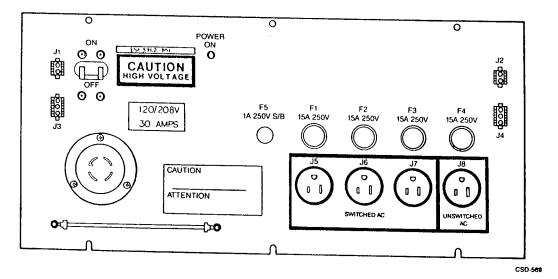

| FIGURE 2-5:                    | 1045 POWER SUPPLY CONVERSION JUMPERS 2-11               |

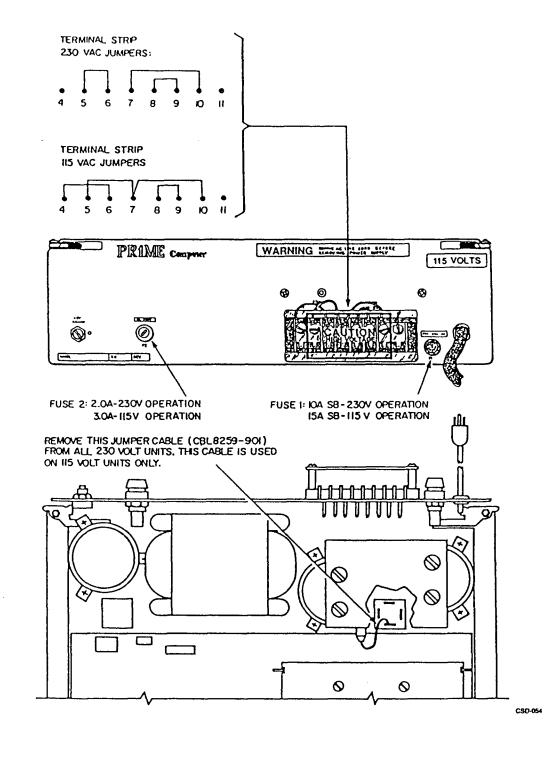

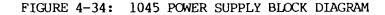

| FIGURE 2-6:                    | 1051 POWER SUPPLY CONVERSION JUMPERS 2-13               |

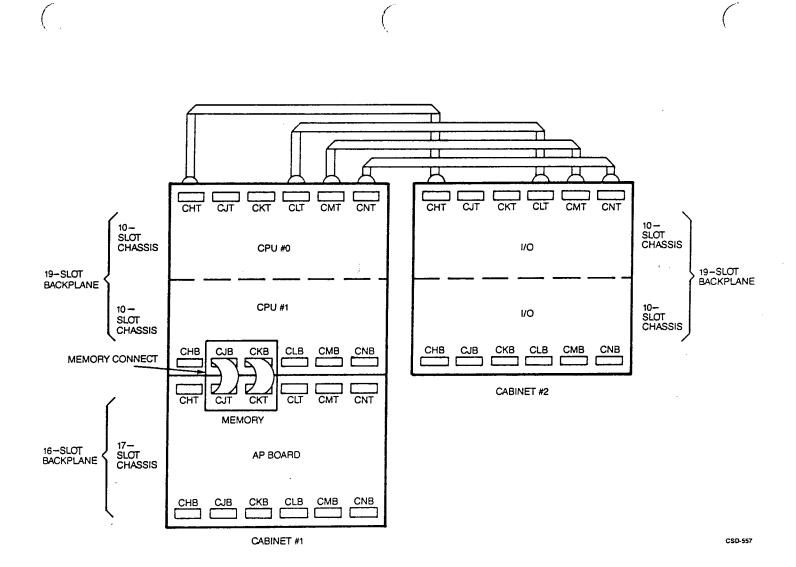

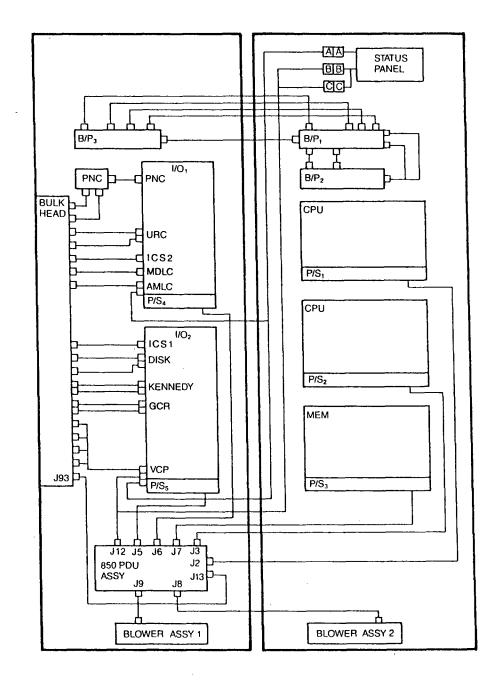

| FIGURE 2-7:                    | DUAL CHASSIS LAYOUT AND CHASSIS INTERCONNECTION 2-15    |

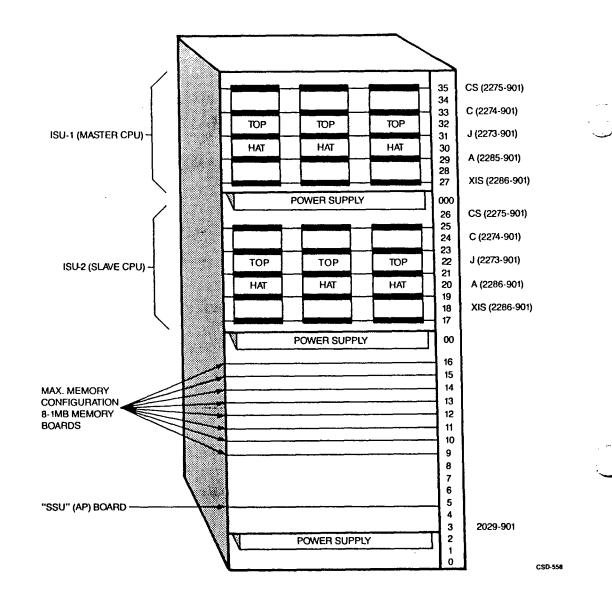

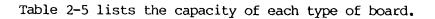

| FIGURE 2-8:                    | 850 MAIN BAY CABINET 2-16                               |

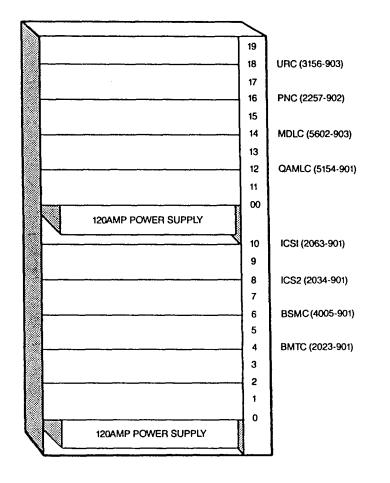

| FIGURE 2-9:                    | 850 I/O CABINET 2-17                                    |

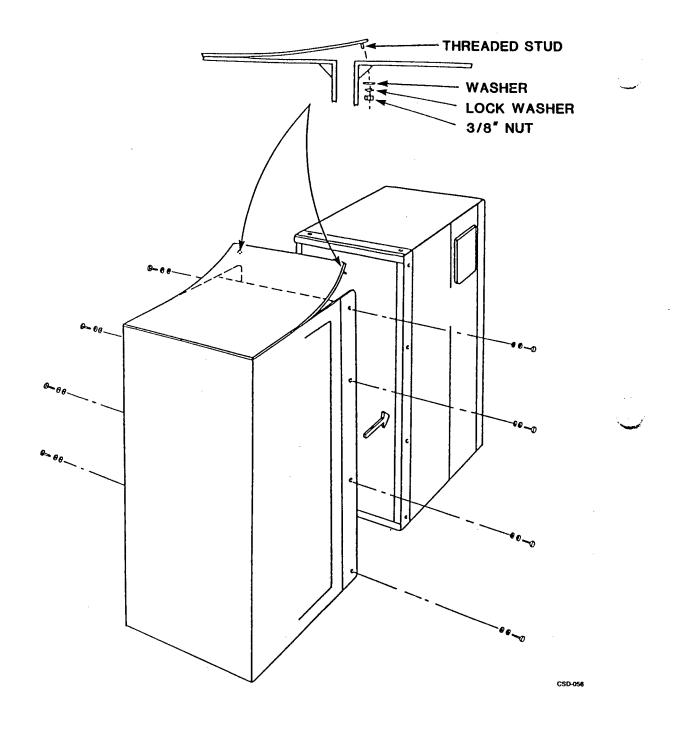

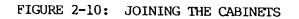

| FIGURE 2-10:                   | JOINING THE CABINETS 2-18                               |

| FIGURE 2-11:                   | LEVELING LEGS 2-19                                      |

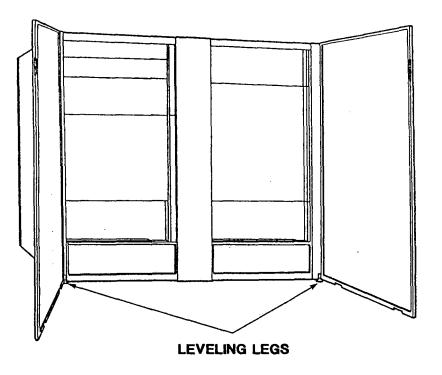

|                                | 850 FCC CABINETS CABLING OVERVIEW                       |

|                                | 550-II CABLING                                          |

| TABLE 2-5:                     | MEMORY BOARD CAPACITY                                   |

| FIGURE 2-14:                   |                                                         |

| TABLE 2-6:                     | 50 SERIES MEMORY ADDRESSING 2-24                        |

| TABLE 2-7:                     | 50 SERIES MEMORY SIZE CONFIGURATIONS - 2.0 MB 2-25      |

| TABLE 2-8:                     | 50 SERIES MEMORY SIZE CONFIGURATIONS - 2.5 MB 2-25      |

| TABLE 2-9:                     | 50 SERIES MEMORY SIZE CONFIGURATIONS - 3.0 MB 2-26      |

| TABLE 2-10:                    | 50 SERIES MEMORY SIZE CONFIGURATIONS - 3.5 MB 2-26      |

| TABLE 2-11:                    |                                                         |

|                                | 50 SERIES MEMORY SIZE CONFIGURATIONS - 4.5 MB 2-27      |

|                                | 50 SERIES MEMORY SIZE CONFIGURATIONS - 5.0 MB 2-27      |

|                                | 50 SERIES MEMORY SIZE CONFIGURATIONS - 5.5 MB 2-28      |

|                                | 50 SERIES MEMORY SIZE CONFIGURATIONS - 6.0 MB 2-28      |

|                                | 50 SERIES MEMORY SIZE CONFIGURATIONS - 6.5 MB 2-28      |

|                                | 50 SERIES MEMORY SIZE CONFIGURATIONS - 7.0 MB 2-28      |

| TABLE $2-18$                   | 50 SERIES MEMORY SIZE CONFIGURATIONS - 8.0 MB 2-29      |

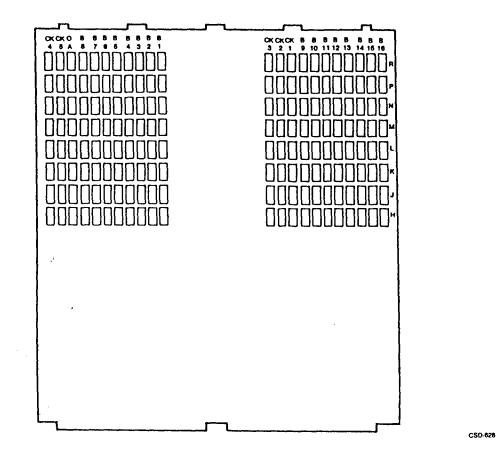

|                                | E6, E7, E8 AND E9 MEMORY BOARD SWITCH SETTINGS 2-29     |

|                                | MEMORY BOARD SWITCHES                                   |

|                                | TYPICAL LAYOUT OF CABLES AND EQUIPMENT                  |

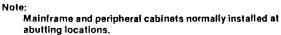

|                                | TYPICAL CABLE CONNECTIONS AT MAINFRAME CABINET 2-32     |

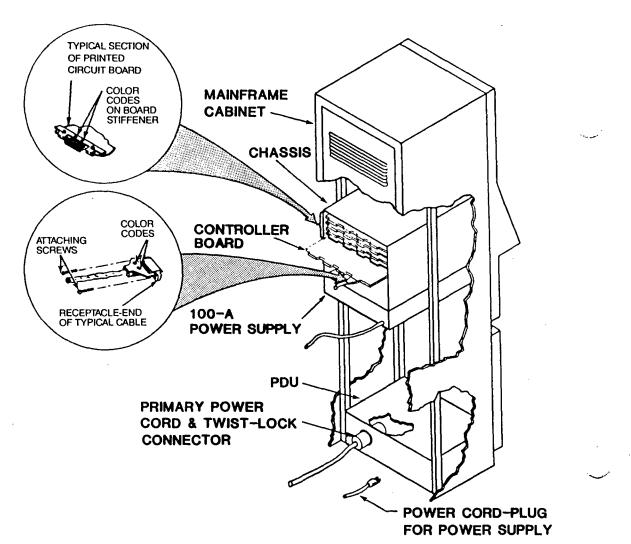

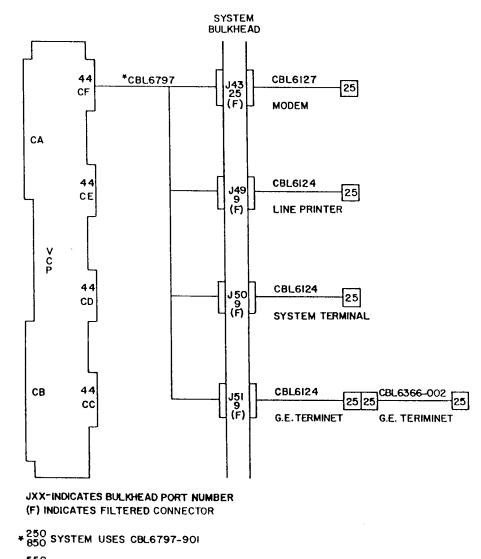

|                                | BULKHEAD PANELS                                         |

|                                | 50 SERIES PRIORITY: BASIC ORDER                         |

|                                | SUMMARY OF 50 SERIES NON-BULKHEAD CABLES                |

|                                | SUMMARY OF 50 SERIES NON-BULKHEAD CABLES                |

|                                | 50 SERIES SPECIAL BULKHEADING CABLES                    |

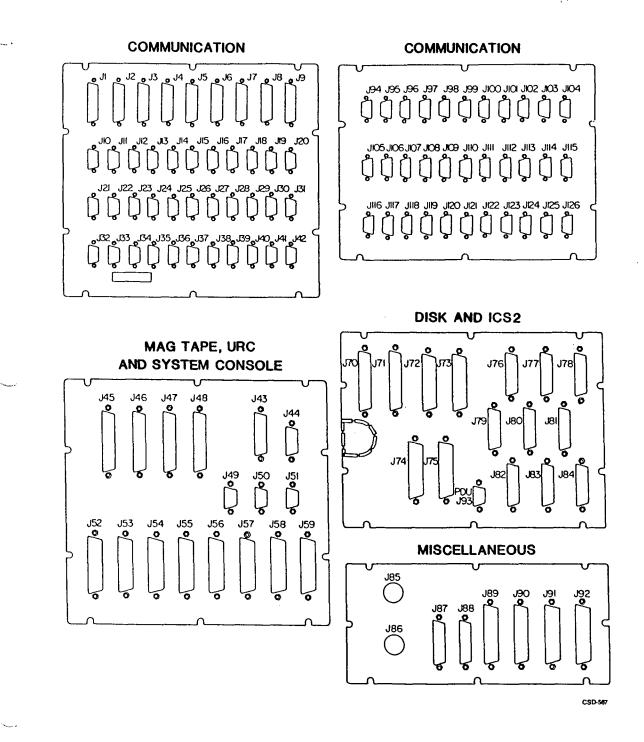

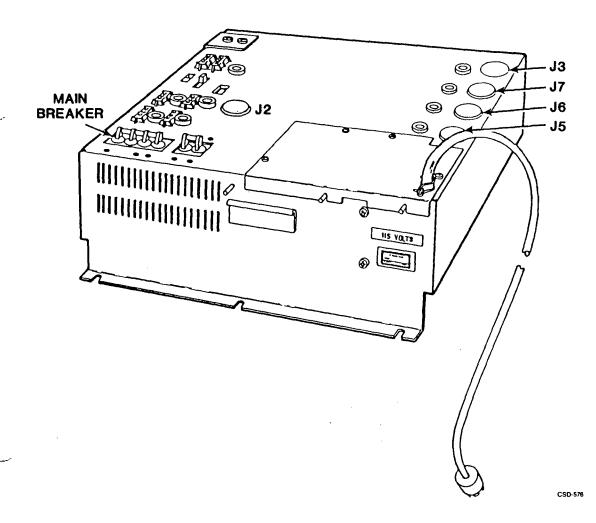

|                                | POWER SUPPLY INSTALLATION                               |

|                                |                                                         |

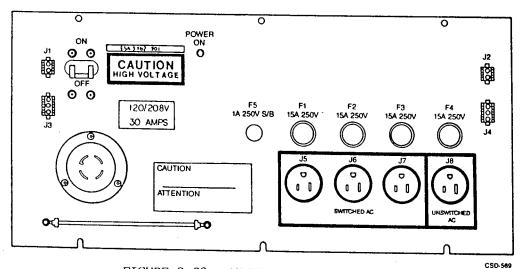

| 1300KE 2-20                    | : MAINFRAME PDU DOMESTIC 2-41                           |

xv

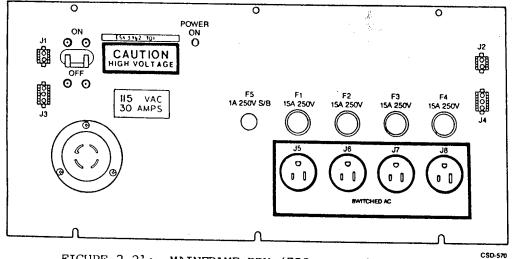

| FIGURE 2-21: | MAINFRAME PDU (750 SYSTEM) DOMESTIC 2-41                  |

|--------------|-----------------------------------------------------------|

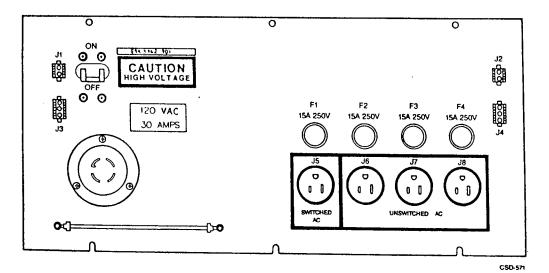

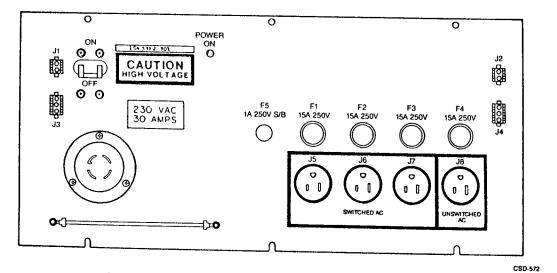

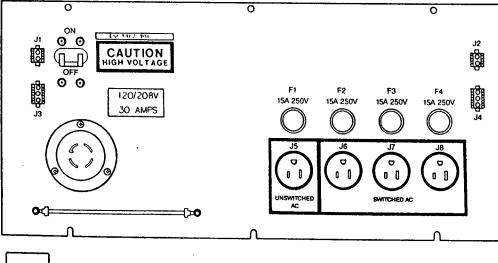

| FIGURE 2-22: | PERIPHERAL PDU DOMESTIC 2-42                              |

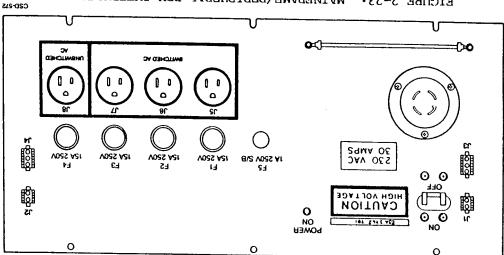

| FIGURE 2-23: | MAINFRAME/PERIPHERAL PDU INTERNATIONAL 2-43               |

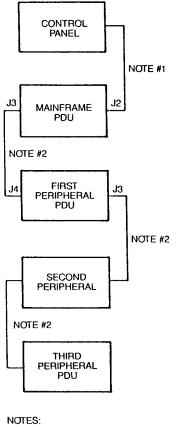

| FIGURE 2-24: | PDU TO PDU INTERCONNECTIONS SINGLE CABINET PROCESSOR 2-44 |

| FIGURE 2-25: | PDU TO PDU INTERCONNECTIONS DUAL CABINET PROCESSOR 2-45   |

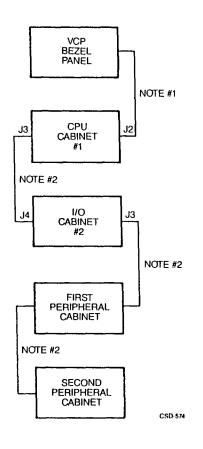

| FIGURE 2-26: | MAIN POWER CABINET INSTALLATION                           |

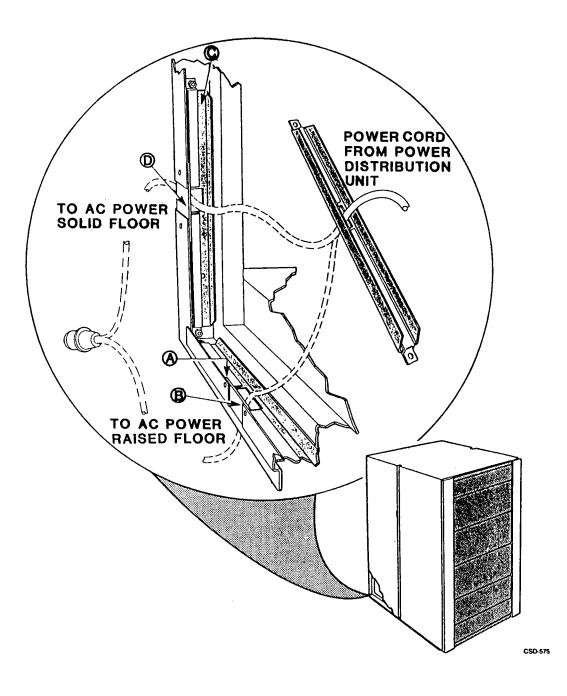

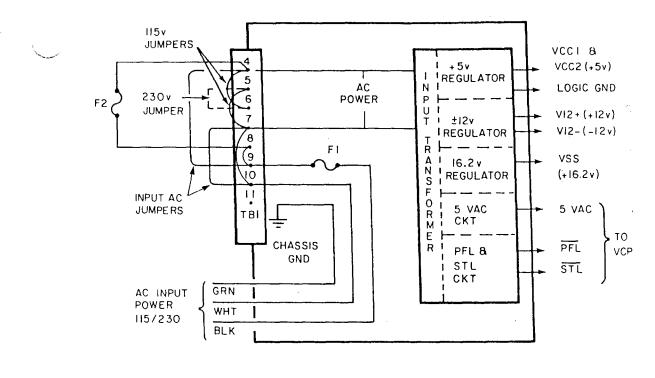

| FIGURE 2-27: | POWER SUPPLY OUTLETS                                      |

| FIGURE 2-28: | VCP CABLING 2-48                                          |

|              | CONTROLLER DEVICE ADDRESSES                               |

|              | 4004 ADDRESS CONVERSION                                   |

|              | DEVICE CONFIGURATION PROMS 2-53                           |

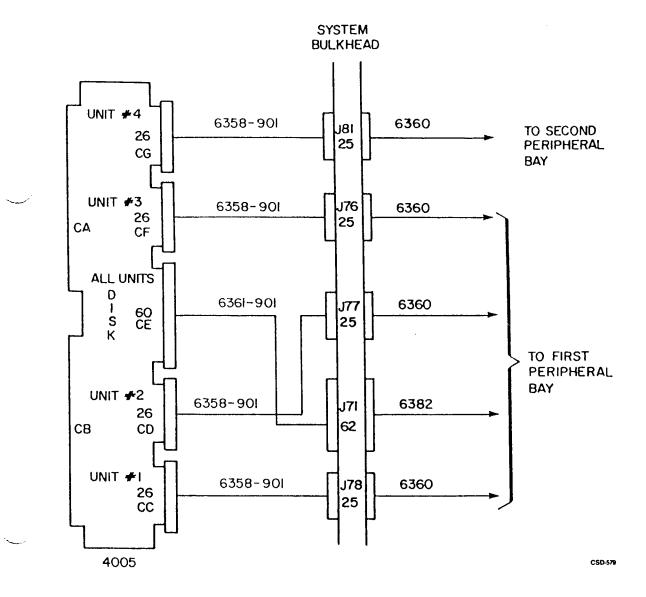

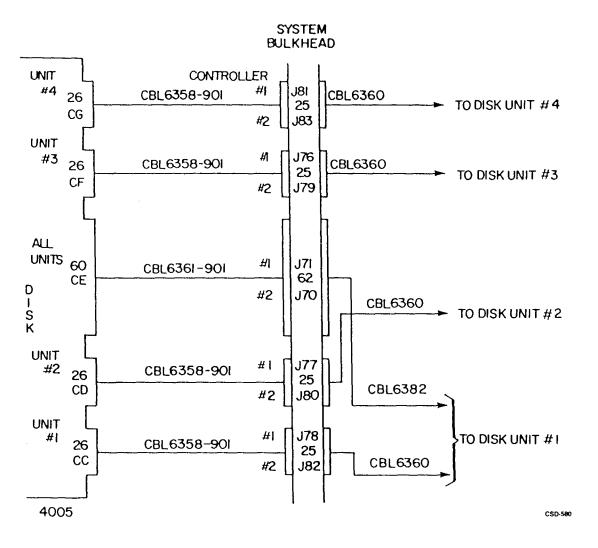

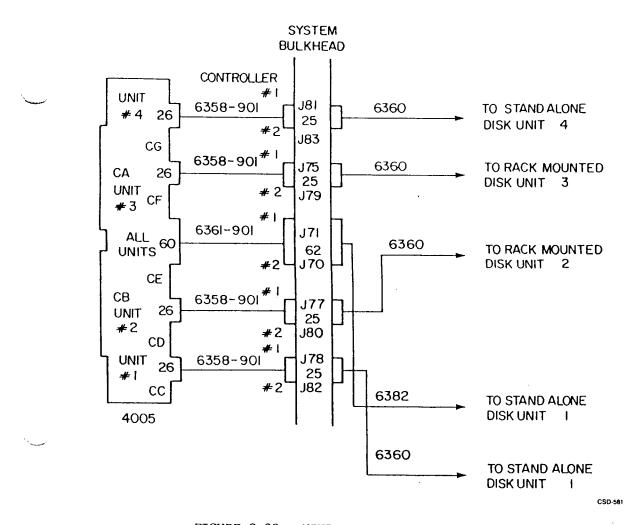

|              | RACK-MOUNTED DISK BULKHEAD CABLING 2-53                   |

|              | STAND-ALONE DISK BULKHEAD CABLING 2-54                    |

|              | MIXED-DISK BULKHEAD CABLING 2-55                          |

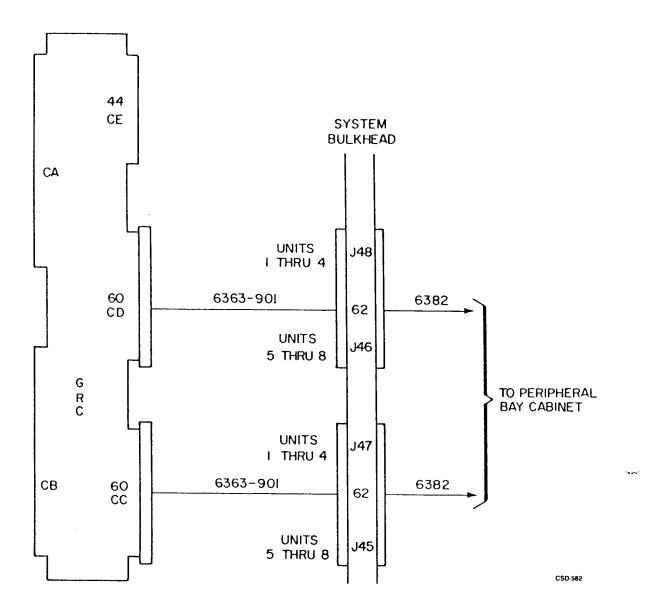

|              | GRC BULKHEAD CABLING                                      |

|              | KENNEDY TAPE CONTROLLER BULKHEAD CABLING 2-57             |

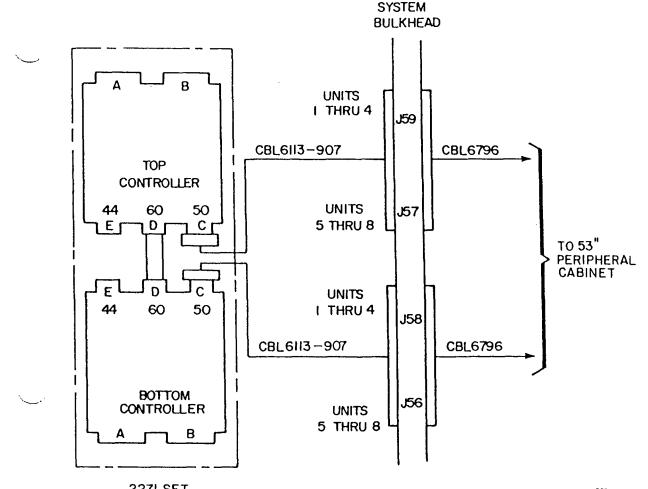

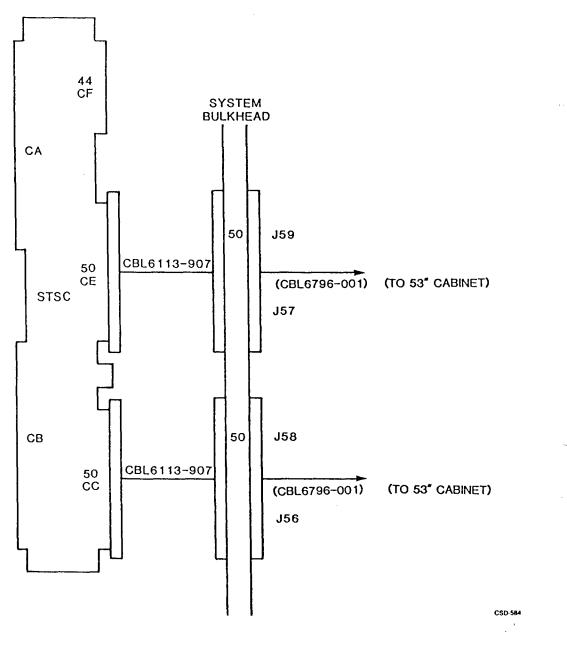

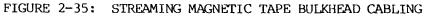

|              | STREAMING MAGNETIC TAPE BULKHEAD CABLING 2-58             |

|              | URC CONFIGURATIONS                                        |

|              | URC BULKHEAD CABLING                                      |

|              | ICS1 ADDRESSES                                            |

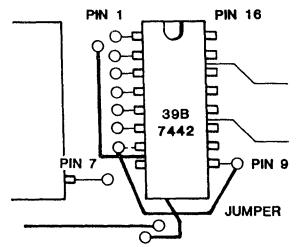

|              | ICS1 ADDRESS JUMPERS 2-62                                 |

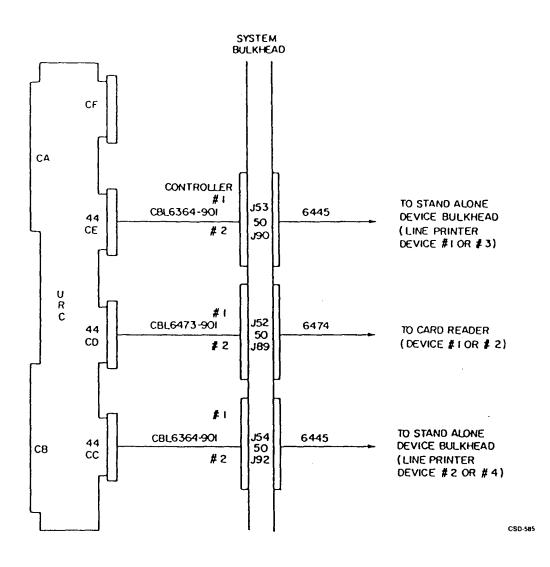

|              | ICS1 BULKHEAD CABLING                                     |

|              | ICS1 CABLE TO BULKHEAD CONFIGURATION 2-63                 |

|              | ICS2 CONTROLLER BOARD OPTIONS                             |

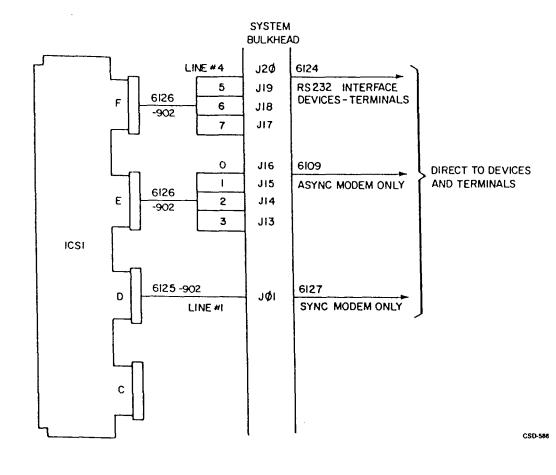

|              | ICS2 BULKHEAD CABLING 2-65                                |

| TABLE 2-31:  | LAC BUS BACKPLANES 2-66                                   |

| TABLE 2-32:  | AMLC ADDRESS JUMPERS 2-67                                 |

| TABLE 2-33:  | AMLC BAUD RATE CONVERSION                                 |

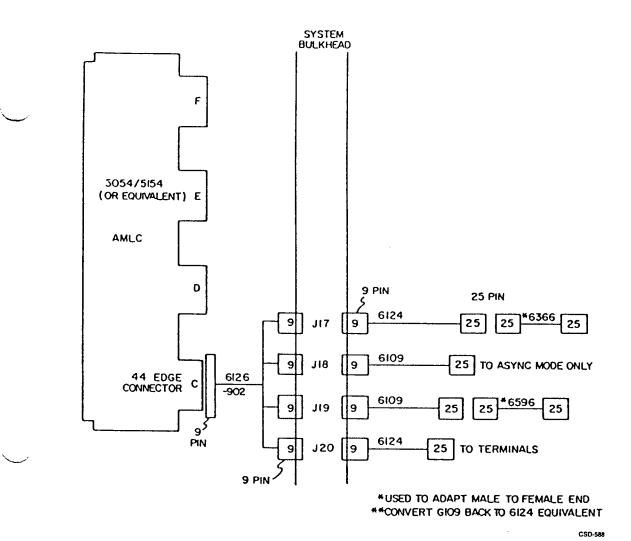

| TABLE 2-34:  | AMLC CABLE TO BULKHEAD CONFIGURATION 2-68                 |

| FIGURE 2-39: | AMLC BULKHEAD CABLING 2-71                                |

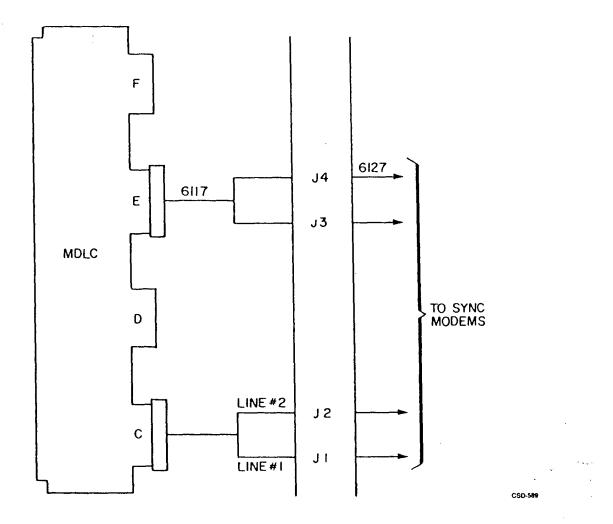

| FIGURE 2-40: | MDLC BULKHEAD CABLING 2-72                                |

| TABLE 2-35:  | MDLC CABLE TO BULKHEAD CONFIGURATION 2-72                 |

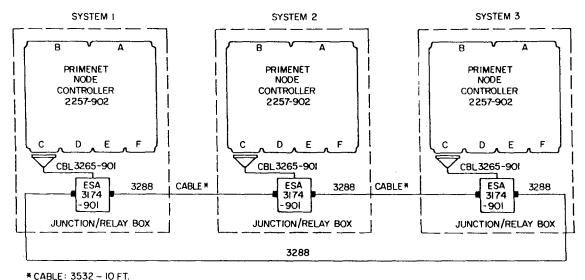

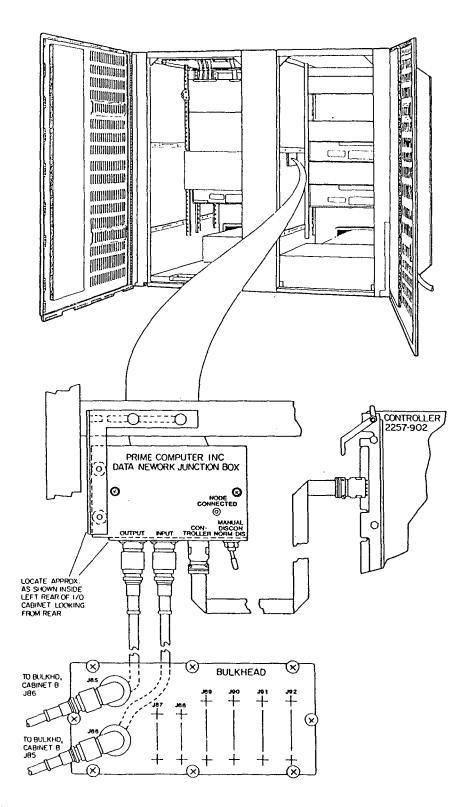

|              | PNC INTERCABLING 2-73                                     |

|              | PNC 50 SERIES CABLING 2-74                                |

| FIGURE 2-43: | MAIN CABINET TO PERIPHERAL CABINET CABLING 2-75           |

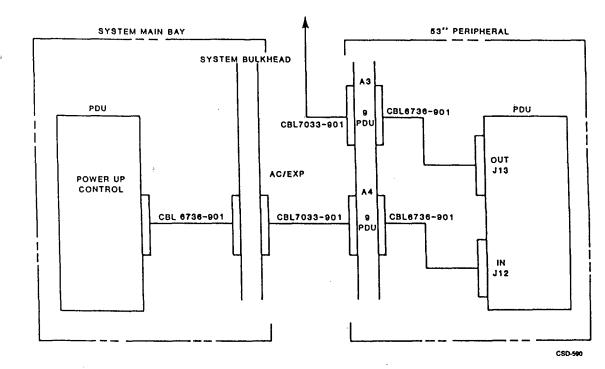

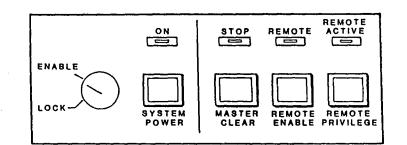

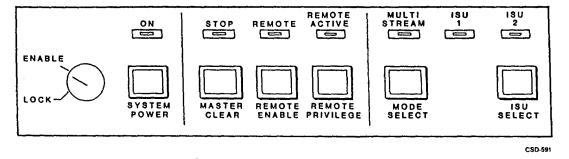

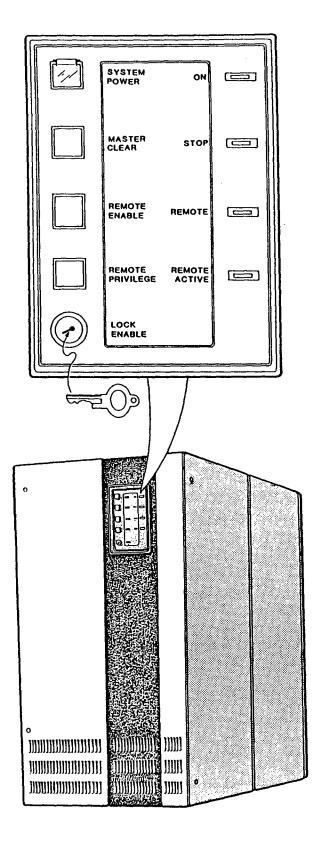

| FIGURE 3-1:  | NON-FCC CABINET STATUS PANELS                             |

| TABLE 3-1:   |                                                           |

| TABLE 3-2:   | SYSTEM STATUS PANEL INDICATORS                            |

| FIGURE 3-2:  | FCC CABINET STATUS PANEL                                  |

| TABLE 3-3:   | SYSTEM STATUS PANEL CONTROLS                              |

| TABLE 3-4:   | STATUS PANEL INDICATORS                                   |

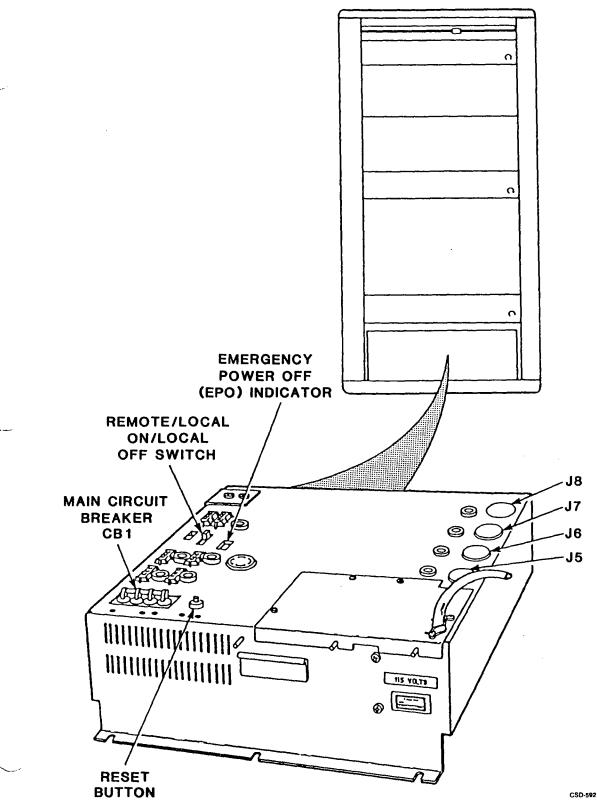

| TABLE 3-5:   | FCC PDU CONTROLS 3-6                                      |

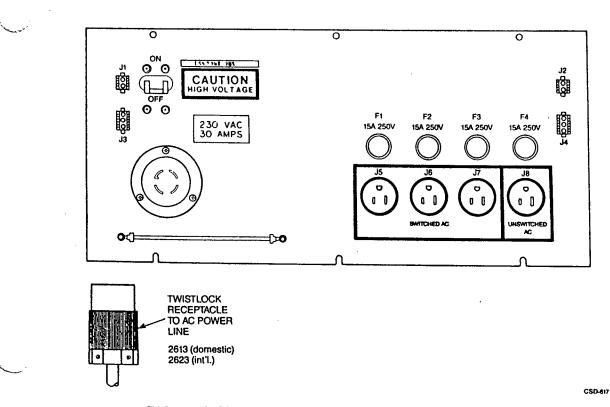

| FIGURE 3-3:  | FCC CABINET PDU                                           |

| TABLE 3-6:   | SENSE SWITCH SETTINGS FOR BOOT                            |

| TABLE 3-7:   | REGISTER FILE LOCATIONS                                   |

| TABLE 3-8:   | KEYS AND MODALS 3-18                                      |

| TABLE 3-9:   | MODALS                                                    |

|              | : VCP REGISTER FILE MNEMONICS                             |

| TABLE 3-11:  | : SSU SWITCH SETTINGS 3-26                                |

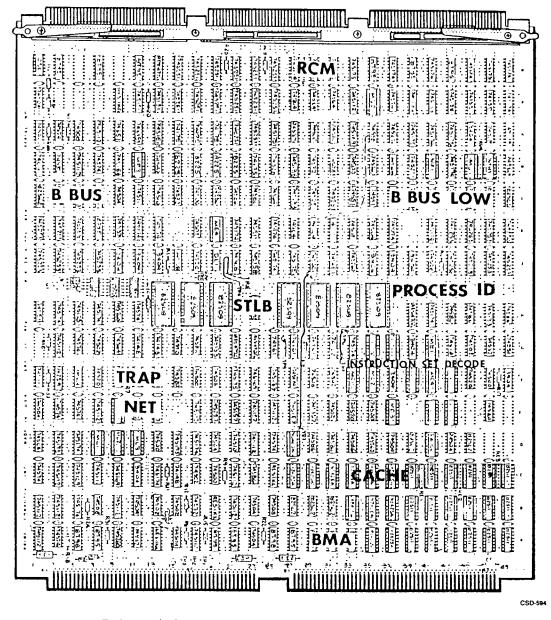

| FIGURE 4-1:  | TWO AND THREE BOARD CPUS: A BOARD 4- 2                    |

| FIGURE 4-2:  | TWO AND THREE BOARD CPUS: B BOARD                         |

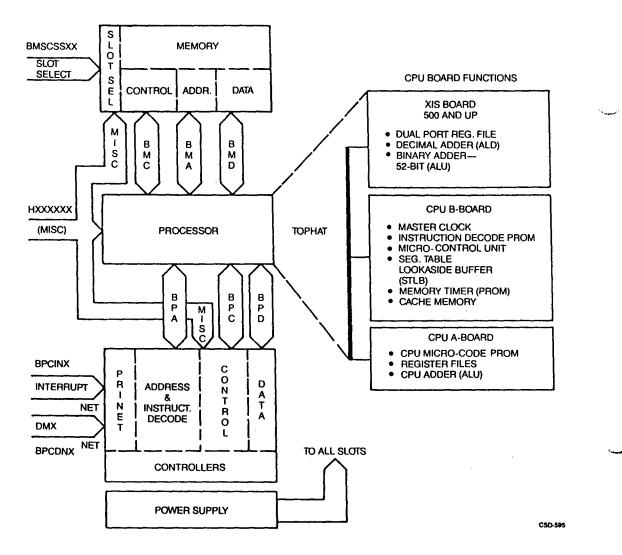

| FIGURE 4-3:  | P550-II, 500, 650, SYSTEMS: CPU BLOCK DIAGRAM 4- 4        |

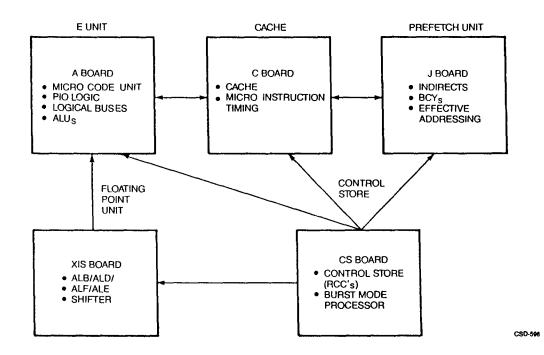

| FIGURE 4-4:  | 750 CPU: FUNCTIONAL BLOCK DIAGRAM                         |

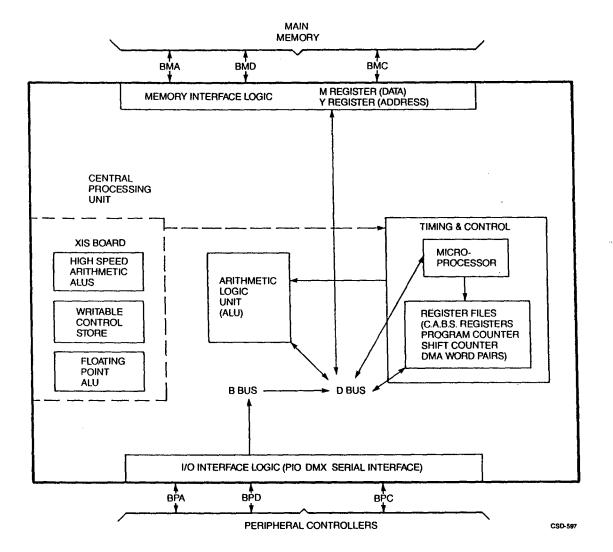

| FIGURE 4-5:  |                                                           |

|              |                                                           |

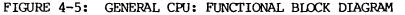

| FIGURE  | 4-6:             | MEMORY ADDRESS TRANSLATION                    | 9   |

|---------|------------------|-----------------------------------------------|-----|

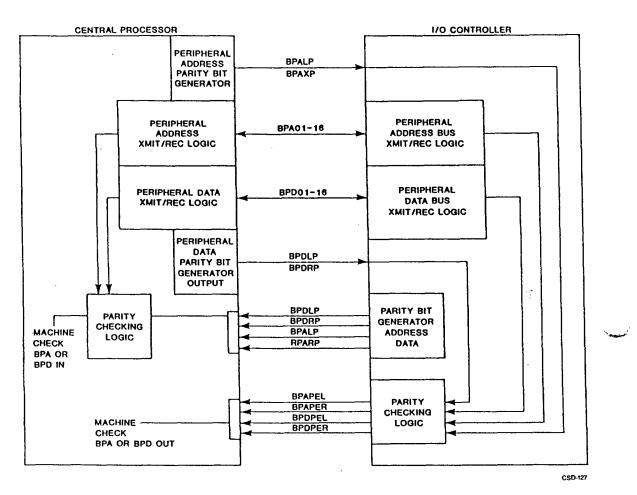

| FIGURE  |                  | PARITY GENERATION AND CHECKING 4-             |     |

| FIGURE  | 4-8:             | INTERRUPT PROGRAM NETWORK                     |     |

| FIGURE  |                  | INTERRUPT PRIORITY NETWORK                    |     |

| FIGURE  | 4-10:            | PIO INSTRUCTION FIELDS                        | 26  |

| TABLE   |                  | BPC MODE LINE SETTINGS                        |     |

| FIGURE  | 4-12:            | DMA TRANSFER                                  | ว้า |

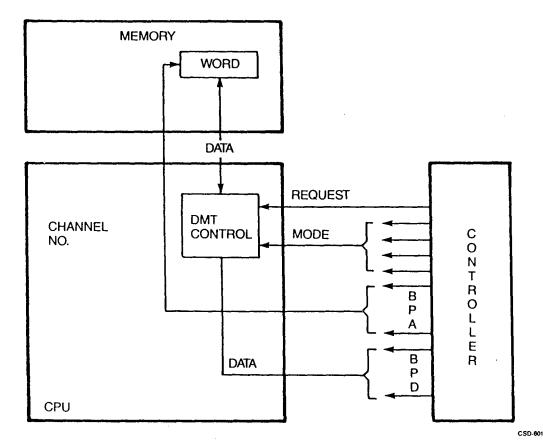

| FIGURE  | 4-13:            | DMT TRANSFER                                  | 33  |

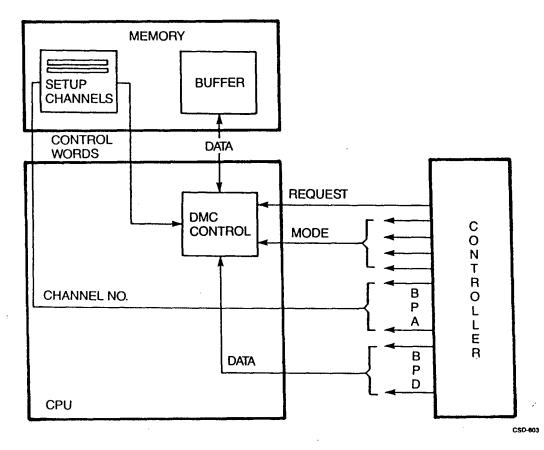

| FIGURE  | 4-15:            | DMC TRANSFER                                  | 36  |

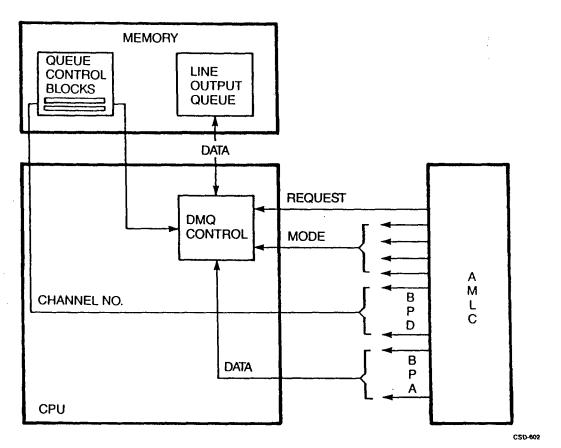

| FIGURE  | 4-16:            | DMQ TRANSFER                                  | 37  |

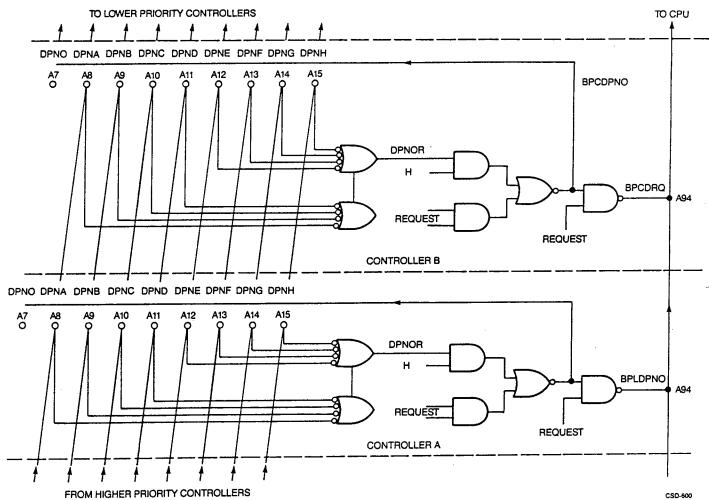

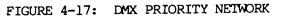

| FIGURE  | 4-17:            | DMX PRIORITY NETWORK                          | 41  |

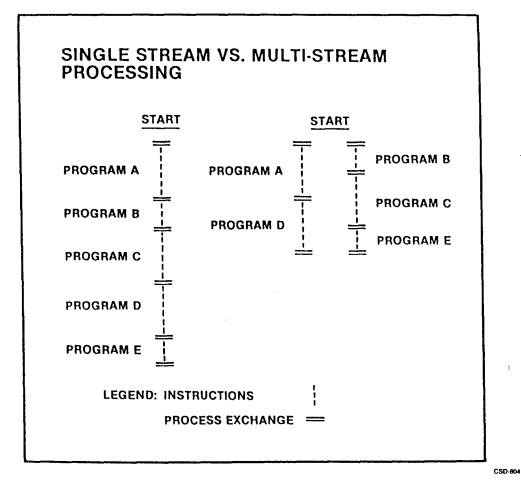

| FIGURE  | 4-18:            | SINGLE STREAM VS. MULTI-STREAM PROCESSOR 4-   | 43  |

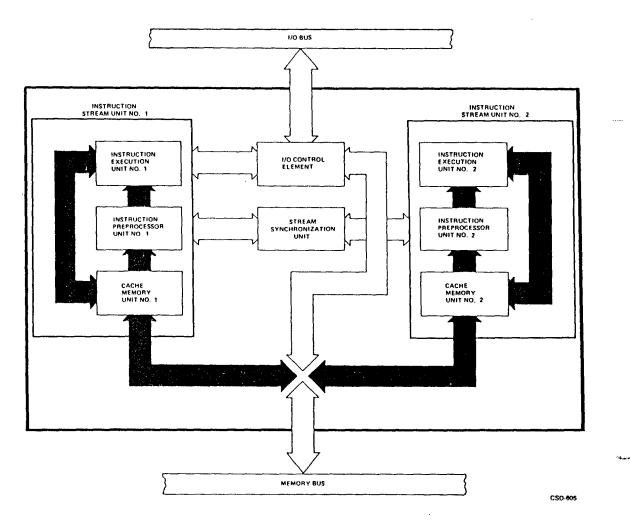

|         |                  | P850 FUNCTIONAL BLOCK DIAGRAM 4-              |     |

|         |                  | SSU ADDRESS SPACE DEFINITION                  |     |

|         |                  | 850 DIAGNOSTIC STATUS MODES                   |     |

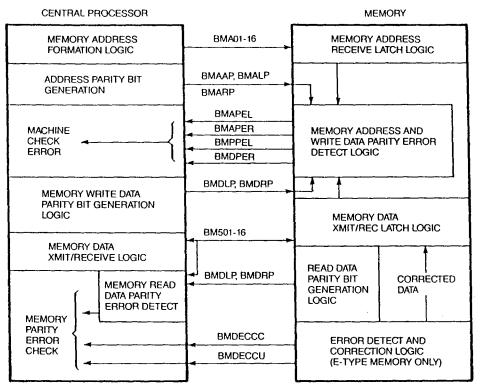

|         |                  | MEMORY INTERFACE ADDRESS AND DATA PATHS 4-    |     |

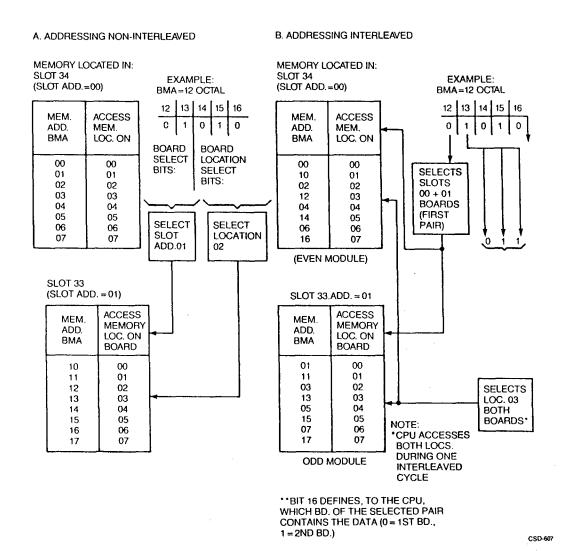

|         |                  | MEMORY ADDRESSING CONCEPTUAL ILLUSTRATIONS 4- |     |

|         |                  | MEMORY BOARD CAPACITY                         |     |

| TABLE   | 4-5:             | MEMORY TYPE SELECTION TO CPU                  | -58 |

|         |                  | SYSTEM ILLUSTRATION (PART ONE)                |     |

| FIGURE  | 4-23:            | SYSTEM ILLUSTRATION (PART TWO, REAR VIEW) 4-  | -60 |

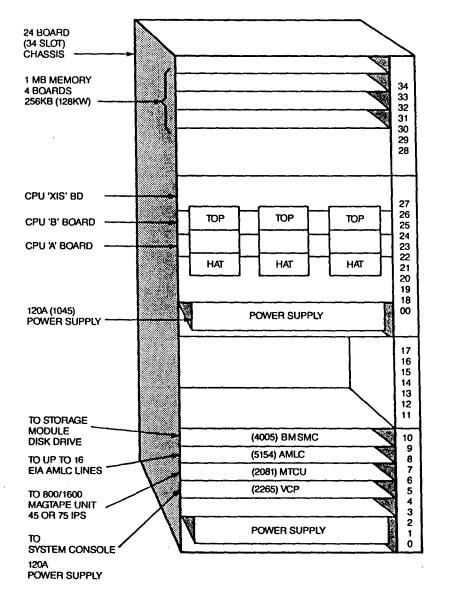

| TABLE   | 4-6:             | SYSTEM SLOTS AND CHASSIS                      | -61 |

| FIGURE  | 4-24:            | 17-SLOT BACKPLANE 4-                          | -62 |

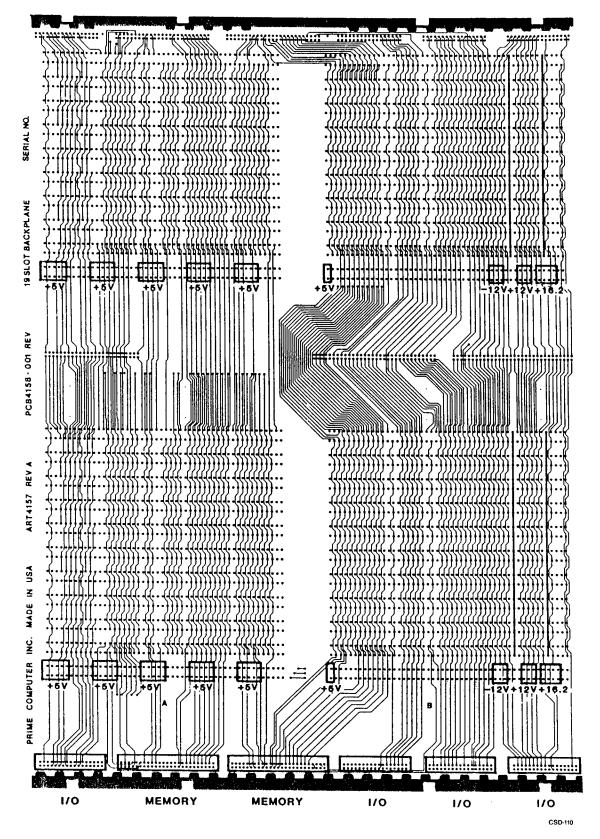

| FIGURE  | 4-25:            | 19-SLOT BACKPLANE 4-                          | -63 |

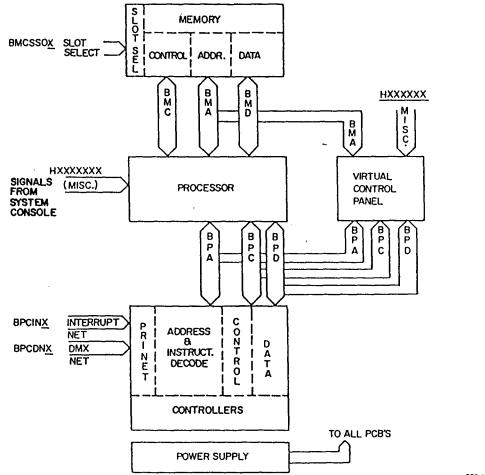

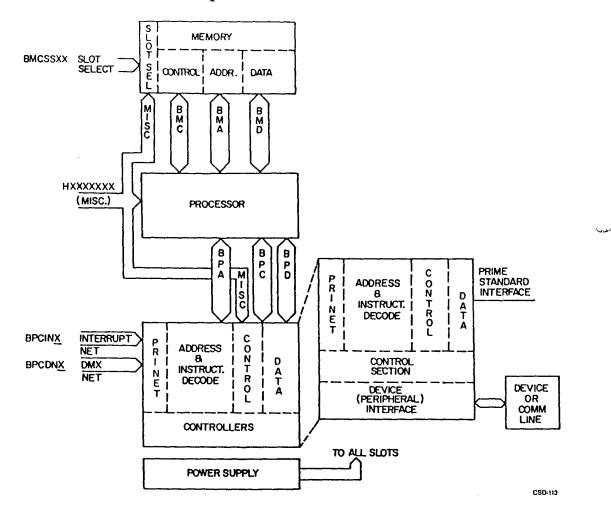

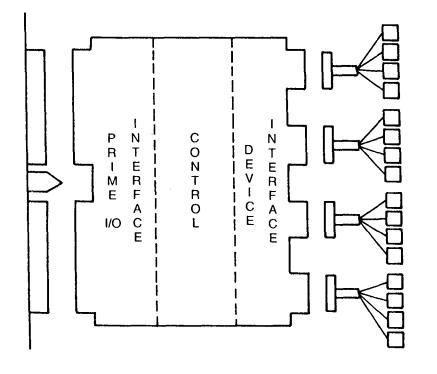

| FIGURE  | 4-26:            | BASIC SYSTEM BLOCK 4-                         | -64 |

| TABLE   | 4-7:             | BACKPLANE SIGNAL LIST 4-                      | -65 |

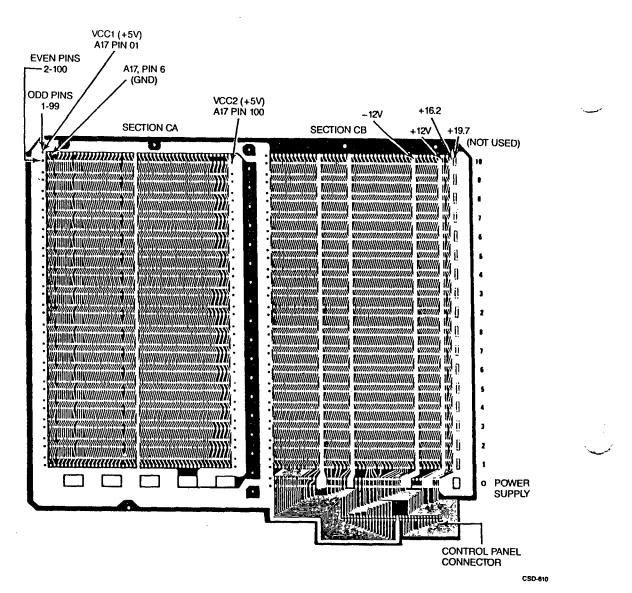

| FIGURE  | 4-27:            | BACKPLANE (SLOT) PIN NUMBER IDENTIFICATION 4- | -71 |

|         |                  | 850 BACKPLANE SIGNAL LIST 4-                  |     |

| FIGURE  | 4-28:            | I/O AND MEMORY BUSES 4-                       | -76 |

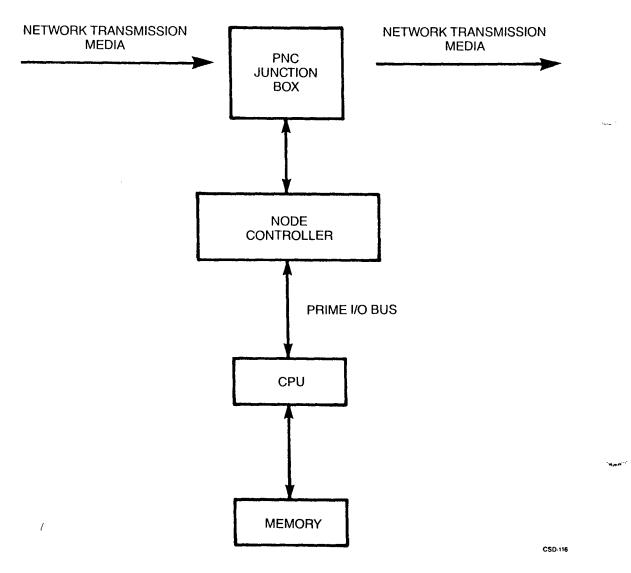

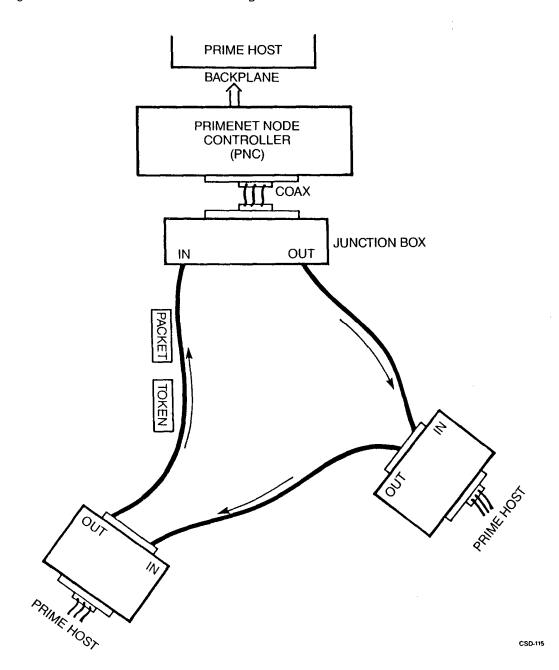

| FIGURE  | 4-29:            | PNC NEIWORK 4-                                | -79 |

| FIGURE  | 4-30:            | PRIMENET NODE DATA FLOW 4-                    | -80 |

| FIGURE  | 4-31:            | AMLC: BASIC DIAGRAM 4-                        | -81 |

| FIGURE  | 4-32:            | VCP BLOCK DIAGRAM 4-                          | -88 |

| TABLE   | 4-9:             | CONNECTOR CA SIGNAL LIST 4                    | -91 |

| TABLE   | 4-10:            | CONNECTOR CB SIGNAL LIST 4                    | -92 |